- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄67987 > MCV18ET-I/SO FLASH, 20 MHz, RISC MICROCONTROLLER, PDSO18 PDF資料下載

參數(shù)資料

| 型號(hào): | MCV18ET-I/SO |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | FLASH, 20 MHz, RISC MICROCONTROLLER, PDSO18 |

| 封裝: | 7.50 MM, LEAD FREE, SOIC-18 |

| 文件頁數(shù): | 25/108頁 |

| 文件大?。?/td> | 1509K |

| 代理商: | MCV18ET-I/SO |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁當(dāng)前第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁

2009 Microchip Technology Inc.

DS41399A-page 23

MCV18E

3.2

PORTB and the TRISB Register

PORTB is an 8-bit wide bidirectional port. The

corresponding data direction register is TRISB. Setting

a TRISB bit (= 1) will make the corresponding PORTB

pin an input (i.e., put the corresponding output driver in

a High-Impedance mode). Clearing a TRISB bit (= 0)

will make the corresponding PORTB pin an output (i.e.,

put the contents of the output latch on the selected pin).

EXAMPLE 3-2:

INITIALIZING PORTB

Each of the PORTB pins has a weak internal pull-up. A

single control bit can turn on all the pull-ups. This is

performed by clearing bit RBPU of the OPTION regis-

ter. The weak pull-up is automatically turned off when

the port pin is configured as an output. The pull-ups are

disabled on a Power-on Reset.

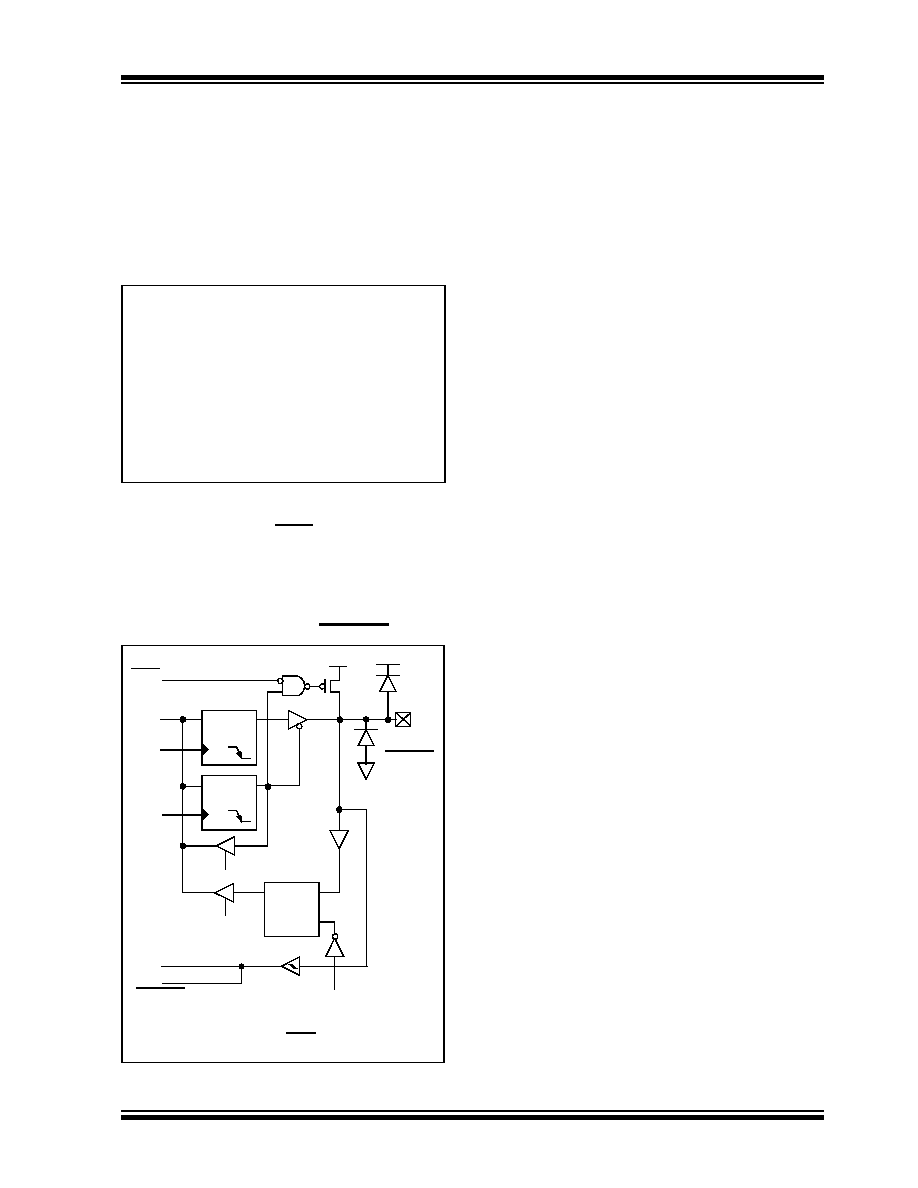

FIGURE 3-3:

BLOCK DIAGRAM OF

RB0/INT/ECCPAS2 PIN

When enabling peripheral functions, care should be

taken in defining TRIS bits for each PORTB pin. Some

peripherals override the TRIS bit to make a pin an

output, while other peripherals override the TRIS bit to

make a pin an input. Since the TRIS bit override is in

effect while the peripheral is enabled, read-modify-

write instructions (such as BSF, BCF, XORWF) with

TRISB as the destination should be avoided. The user

should refer to the corresponding peripheral section for

the correct TRIS bit settings.

Four of PORTB’s pins, RB<7:4>, have an interrupt-on-

change feature. Only pins configured as inputs can

cause this interrupt to occur (i.e., any RB<7:4> pin

configured as an output is excluded from the interrupt-

on-change comparison). The input pins, RB<7:4>, are

compared with the old value latched on the last read of

PORTB. The “mismatch” outputs of RB<7:4> are

OR’ed together to generate the RB Port Change

Interrupt with flag bit RBIF of the INTCON register.

This interrupt can wake the device from Sleep. The

user, in the Interrupt Service Routine, can clear the

interrupt in the following manner:

1.

Perform a read of PORTB to end the mismatch

condition.

2.

Clear flag bit RBIF.

A mismatch condition will continue to set flag bit RBIF.

Reading PORTB will end the mismatch condition and

allow flag bit RBIF to be cleared.

The interrupt-on-change feature is recommended for

wake-up on key depression operation and operations

where PORTB is only used for the interrupt-on-change

feature. Polling of PORTB is not recommended while

using the interrupt-on-change feature.

BCF

STATUS, RP0

;select Bank 0

CLRF

PORTB

;Initialize PORTB by

;clearing output

;data latches

BSF

STATUS, RP0

;Select Bank 1

MOVLW

0xCF

;Value used to

;initialize data

;direction

MOVWF

TRISB

;Set RB<3:0> as inputs

;RB<5:4> as outputs

;RB<7:6> as inputs

Data Latch

RBPU(1)

P

VDD

Q

D

CK

Q

D

CK

QD

EN

DATA

WR

RD TRIS

RD PORT

weak

pull-up

RD PORT

RB0/INT

TTL

Input

Buffer

Schmitt Trigger

Buffer

TRIS Latch

Note

1:

To enable weak pull-ups, set the appropriate TRIS

bit(s) and clear the RBPU bit (OPTION register).

VSS

VDD

BUS

PORT

TRIS

ECCPAS2: ECCP Auto-shutdown input

RB0/

INT/

ECCPAS2

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MCV18E-I/P | 32-BIT, FLASH, 20 MHz, RISC MICROCONTROLLER, PDIP18 |

| MD8086-2/B | 16-BIT, 8 MHz, MICROPROCESSOR, CDIP40 |

| MD80C154-12/883D | 8-BIT, 12 MHz, MICROCONTROLLER, CDIP40 |

| MR83C154TXXX-20/883 | 8-BIT, MROM, 20 MHz, MICROCONTROLLER, CQCC44 |

| MR83C154XXX-20/883D | 8-BIT, MROM, 20 MHz, MICROCONTROLLER, CQCC44 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MC-V190H | 制造商:Panasonic Industrial Company 功能描述:FILTER KIT |

| M-CV193H | 制造商:Panasonic Industrial Company 功能描述:OD005 |

| MC-V193H | 制造商:Panasonic Industrial Company 功能描述:FILTER KIT |

| MCV19ES | 制造商:Mencom 功能描述: |

| MCV-19FP-FW | 制造商:Mencom 功能描述: |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。