- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄98013 > MCIMX281AVM4B (FREESCALE SEMICONDUCTOR INC) 32-BIT, 454 MHz, RISC PROCESSOR, PBGA289 PDF資料下載

參數(shù)資料

| 型號(hào): | MCIMX281AVM4B |

| 廠商: | FREESCALE SEMICONDUCTOR INC |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | 32-BIT, 454 MHz, RISC PROCESSOR, PBGA289 |

| 封裝: | 14 X 14 MM, 0.80 MM PITCH, ROHS COMPLIANT, PLASTIC, MAPBGA-289 |

| 文件頁(yè)數(shù): | 40/72頁(yè) |

| 文件大小: | 915K |

| 代理商: | MCIMX281AVM4B |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)當(dāng)前第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)

i.MX28 Applications Processors Data Sheet for Automotive Products, Rev. 1

Freescale Semiconductor

45

3.5.9

Inter IC (I2C) Timing

The I2C module is designed to support up to 400-Kbps I2C connection compliant with I2C bus protocol.

The following section describes I2C SDA and SCL signal timings.

(IC1–IC11) shown in the figure.

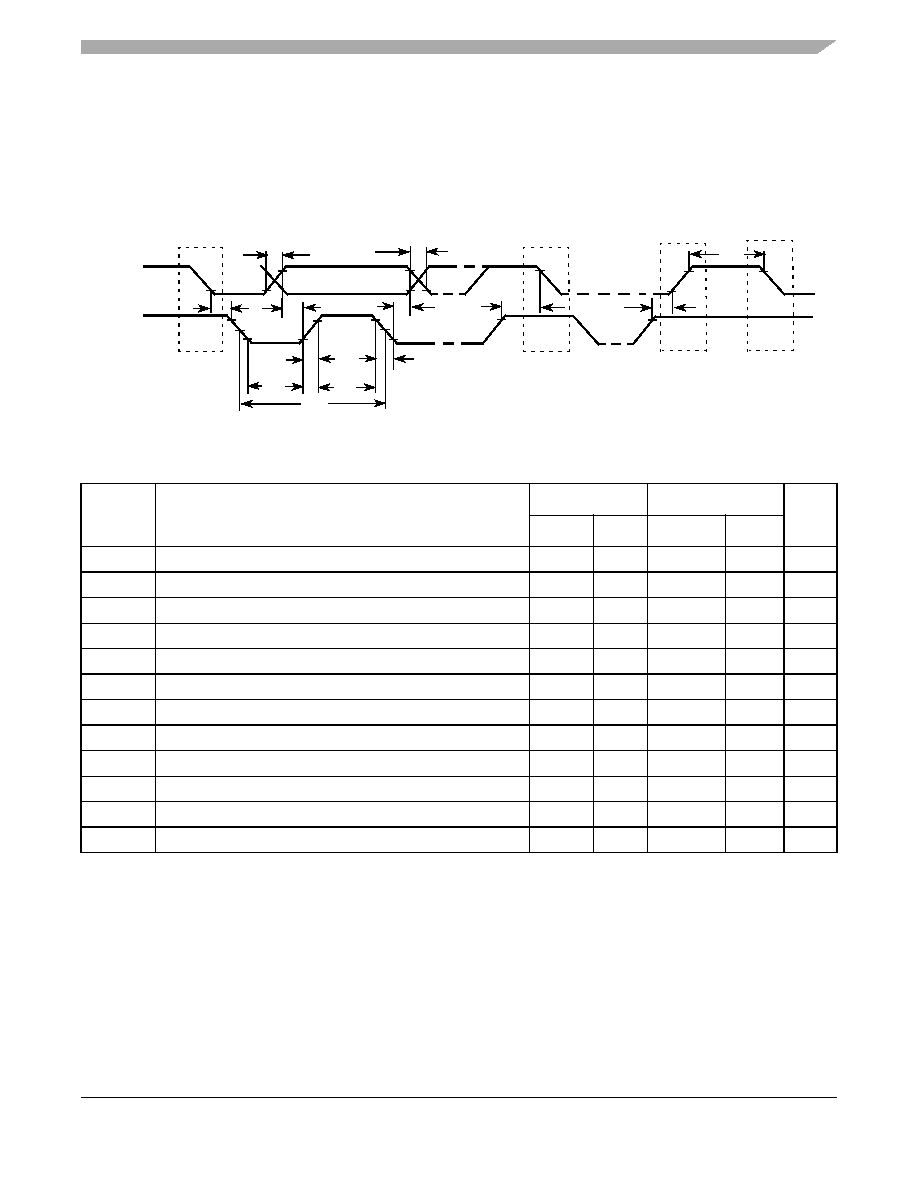

Figure 25. I2C Module Timing Diagram

Table 50. I2C Module Timing Parameters: 1.8 V

– 3.6 V

ID

Parameter

Standard Mode

Fast Mode

Unit

Min.

Max.

Min.

Max.

IC1

I2C_SCL cycle time

10

—

2.5

—

μs

IC2

Hold time (repeated) START condition

4.0

—

0.6

—

μs

IC3

Set-up time for STOP condition

4.0

—

0.6

—

μs

IC4

Data hold time

01

1 A device must internally provide a hold time of at least 300 ns for the I2C_SDA signal in order to bridge the undefined region

of the falling edge of I2C_SCL.

3.452

2 The maximum IC4 has to be met only if the device does not stretch the LOW period (ID no IC5) of the I2C_SCL signal.

μs

IC5

HIGH Period of I2C_SCL clock

4.0

—

0.6

—

μs

IC6

LOW Period of the I2C_SCL clock

4.7

—

1.3

—

μs

IC7

Set-up time for a repeated START condition

4.7

—

0.6

—

μs

IC8

Data set-up time

250

—

1003

3 A fast-mode I2C bus device can be used in a standard-mode I2C bus system, but the requirement of Set-up time (ID No IC7)

of 250 ns must then be met. This is automatically the case if the device does not stretch the LOW period of the I2C_SCL signal.

If such a device does stretch the LOW period of the I2C_SCL signal, it must output the next data bit to the I2C_SDA line

max_rise_time (ID No IC9) + data_setup_time (ID No IC7) = 1000 + 250 = 1250 ns (according to the standard-mode I2C bus

specification) before the I2C_SCL line is released.

—ns

IC9

Bus free time between a STOP and START condition

4.7

—

1.3

—

μs

IC10

Rise time of both I2C_SDA and I2C_SCL signals

—

1000

20+0.1Cb

4

4 C

b = total capacitance of one bus line in pF.

300

ns

IC11

Fall time of both I2C_SDA and I2C_SCL signals

—

300

20+0.1Cb

300

ns

IC12

Capacitive load for each bus line (Cb)

—

400

—

400

pF

IC10

IC11

IC9

IC2

IC8

IC4

IC7

IC3

IC6

IC10

IC5

IC11

START

STOP

START

I2C_SDA

I2C_SCL

IC1

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MCP25020-I/P | SPECIALTY MICROPROCESSOR CIRCUIT, PDIP14 |

| MCP25050T-E/SL | SPECIALTY MICROPROCESSOR CIRCUIT, PDSO14 |

| MCP25055-I/SL | SPECIALTY MICROPROCESSOR CIRCUIT, PDSO14 |

| MCP2510T-E/P | 2 CHANNEL(S), 1M bps, LOCAL AREA NETWORK CONTROLLER, PDIP18 |

| MCZ33781EK | SPECIALTY MICROPROCESSOR CIRCUIT, PDSO32 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MCIMX283CVM4B | 功能描述:處理器 - 專門應(yīng)用 CATSKILLS REV 1.2 RoHS:否 制造商:Freescale Semiconductor 類型:Multimedia Applications 核心:ARM Cortex A9 處理器系列:i.MX6 數(shù)據(jù)總線寬度:32 bit 最大時(shí)鐘頻率:1 GHz 指令/數(shù)據(jù)緩存: 數(shù)據(jù) RAM 大小:128 KB 數(shù)據(jù) ROM 大小: 工作電源電壓: 最大工作溫度:+ 95 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:MAPBGA-432 |

| MCIMX283CVM4BR2 | 功能描述:處理器 - 專門應(yīng)用 Catskills Rev1.2 RoHS:否 制造商:Freescale Semiconductor 類型:Multimedia Applications 核心:ARM Cortex A9 處理器系列:i.MX6 數(shù)據(jù)總線寬度:32 bit 最大時(shí)鐘頻率:1 GHz 指令/數(shù)據(jù)緩存: 數(shù)據(jù) RAM 大小:128 KB 數(shù)據(jù) ROM 大小: 工作電源電壓: 最大工作溫度:+ 95 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:MAPBGA-432 |

| MCIMX283DJM4A | 制造商:Freescale Semiconductor 功能描述:CATSKILLS REV 1.1 - Trays 制造商:Freescale Semiconductor 功能描述:IC MCU 32BIT ROMLESS 289MAPBGA |

| MCIMX283DVM4B | 功能描述:處理器 - 專門應(yīng)用 CATSKILLS REV 1.2 RoHS:否 制造商:Freescale Semiconductor 類型:Multimedia Applications 核心:ARM Cortex A9 處理器系列:i.MX6 數(shù)據(jù)總線寬度:32 bit 最大時(shí)鐘頻率:1 GHz 指令/數(shù)據(jù)緩存: 數(shù)據(jù) RAM 大小:128 KB 數(shù)據(jù) ROM 大小: 工作電源電壓: 最大工作溫度:+ 95 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:MAPBGA-432 |

| MCIMX285AJM4A | 制造商:Freescale Semiconductor 功能描述:CATSKILLS REV 1.1 - Bulk |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。