- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄377885 > MB814265-70 (Fujitsu Limited) CMOS 256K ×16 BIT Hyper Page Mode Dynamic RAM(CMOS 256K ×16 位超級(jí)頁(yè)面存取模式動(dòng)態(tài)RAM) PDF資料下載

參數(shù)資料

| 型號(hào): | MB814265-70 |

| 廠商: | Fujitsu Limited |

| 英文描述: | CMOS 256K ×16 BIT Hyper Page Mode Dynamic RAM(CMOS 256K ×16 位超級(jí)頁(yè)面存取模式動(dòng)態(tài)RAM) |

| 中文描述: | 的CMOS 256K × 16位的超頁(yè)模式動(dòng)態(tài)RAM的CMOS(256K × 16位超級(jí)頁(yè)面存取模式動(dòng)態(tài)內(nèi)存) |

| 文件頁(yè)數(shù): | 1/28頁(yè) |

| 文件大?。?/td> | 364K |

| 代理商: | MB814265-70 |

當(dāng)前第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)

1

DS05-10180-2E

FUJITSU SEMICONDUCTOR

DATA SHEET

MEMORY

CMOS 256K

HYPER PAGE MODE DYNAMIC RAM

×

16 BIT

MB814265-60/-70

CMOS 262,144

×

16 BIT Hyper Page Mode Dynamic RAM

I

DESCRIPTION

The Fujitsu MB814265 is a fully decoded CMOS Dynamic RAM (DRAM) that contains 4,194,304 memory cells

accessible in 16-bit increments. The MB814265 features the “hyper page” mode of operation which provides

extended valid time for data output and higher speed random access of up to 512

same row than the fast page mode. The MB814265-60/-70 DRAMs are ideally suited for memory applications

such as embedded control, buffer, portable computers, and video imaging equipment where very low power

dissipation and high bandwidth are basic requirements of the design.

×

16-bits of data within the

The MB814265 is fabricated using silicon gate CMOS and Fujitsu’s advanced four-layer polysilicon process. This

process, coupled with three-dimensional stacked capacitor memory cells, reduces the possibility of soft errors

and extends the time interval between memory refreshes.

I

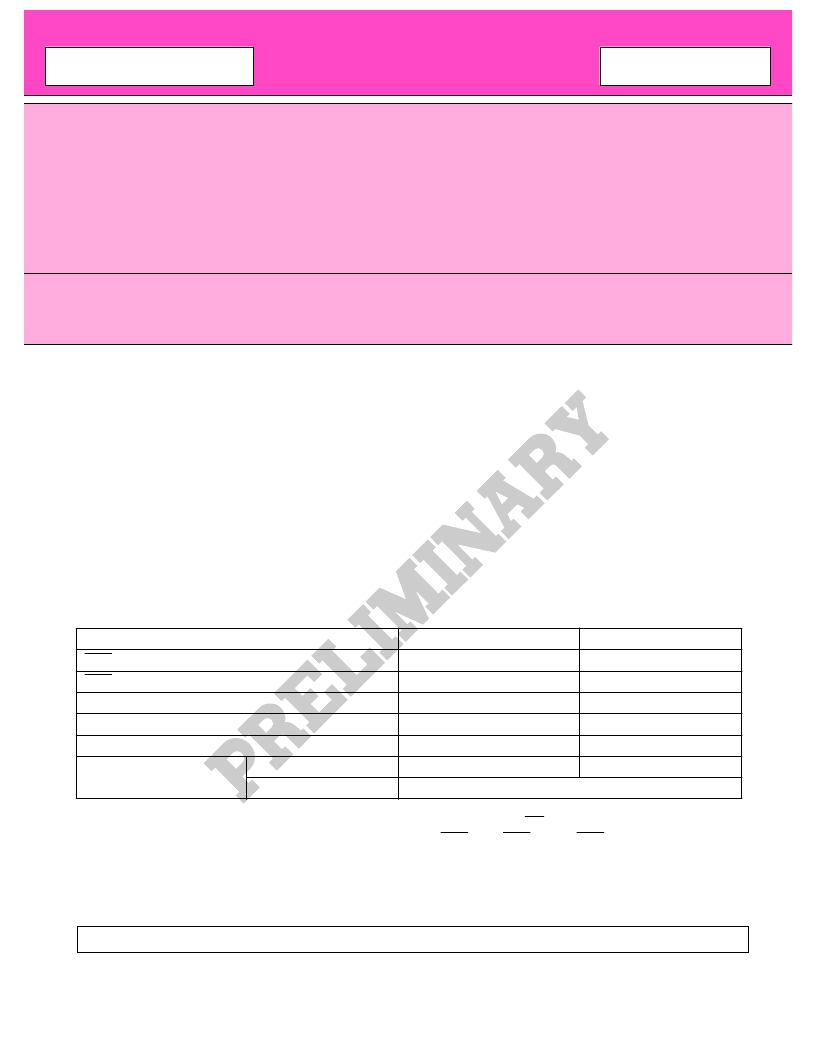

PRODUCT LINE & FEATURES

Parameter

MB814265-60

60 ns max.

20 ns max.

30 ns max.

104 ns max.

25 ns min.

523 mW max.

11 mW max. (TTL level)/5.5 mW max. (CMOS level)

MB814265-70

70 ns max.

20 ns max.

35 ns max.

119 ns min.

30 ns min.

462 mW max.

RAS Access Time

CAS Access Time

Address Access Time

Random Cycle Time

Hyper Page Mode Cycle Time

Low Power Dissipation

Operating current

Standby current

262,144 words

×

16 bit organization

Silicon gate, CMOS, Advanced Stacked

Capacitor Cell

All input and output are TTL compatible

512 refresh cycles every 8.2 ms

9 rows

×

9 columns, addressing scheme

This device contains circuitry to protect the inputs against damage due to high static voltages or electric fields. However, it is advised that normal precautions be

taken to avoid application of any voltage higher than maximum rated voltages to this high impedance circuit.

Early Write or OE controlled Write capability

RAS-only, CAS-before-RAS, or Hidden Refresh

Hyper page mode, Read-Modify-Write capability

On chip substrate bias generator for high

performance

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MB814400A-60 | CMOS 4 M ×1 BIT Fast Page Mode DRAM(CMOS 4M ×1 位快速頁(yè)面存取模式動(dòng)態(tài)RAM) |

| MB814400A-70 | CMOS 4 M ×1 BIT Fast Page Mode DRAM(CMOS 4M ×1 位快速頁(yè)面存取模式動(dòng)態(tài)RAM) |

| MB814400A-80 | CMOS 4 M ×1 BIT Fast Page Mode DRAM(CMOS 4M ×1 位快速頁(yè)面存取模式動(dòng)態(tài)RAM) |

| MB814400C-60 | CMOS 1 M ×4BIT Fast Page Mode DRAM(CMOS 1 M ×4 位快速頁(yè)面存取模式動(dòng)態(tài)RAM) |

| MB814400C-70 | CMOS 1 M ×4 BIT Fast Page Mode DRAM(CMOS 1 M ×4 位快速頁(yè)面存取模式動(dòng)態(tài)RAM) |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MB814400C-70PJN | 制造商:FUJITSU 功能描述:Dynamic RAM, Fast Page, 1M x 4, 26 Pin, Plastic, SOJ |

| MB814405D-60PJN | 制造商:FUJITSU Component Ltd 功能描述: |

| MB8146112 | 制造商:FUJITSU 功能描述:* |

| MB81461-12PSZ | 制造商:FUJITSU 功能描述:VRAM, FAST PAGE, 64KX4, 24 Pin, Plastic, ZIP |

| MB81461B-12 | 制造商:FUJITSU 功能描述: 制造商:FUGITSU 功能描述:81461B-12 制造商:FUJITSU 功能描述:81461B-12 |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。