- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄359059 > M37281MAH-XXXSP (Renesas Technology Corp.) SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER with CLOSED CAPTION DECODER and ON-SCREEN DISPLAY CONTROLLER PDF資料下載

參數(shù)資料

| 型號(hào): | M37281MAH-XXXSP |

| 廠商: | Renesas Technology Corp. |

| 英文描述: | SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER with CLOSED CAPTION DECODER and ON-SCREEN DISPLAY CONTROLLER |

| 中文描述: | 單芯片8位CMOS微機(jī)隱蔽字幕解碼器和屏幕顯示控制器 |

| 文件頁(yè)數(shù): | 81/172頁(yè) |

| 文件大?。?/td> | 1319K |

| 代理商: | M37281MAH-XXXSP |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)第75頁(yè)第76頁(yè)第77頁(yè)第78頁(yè)第79頁(yè)第80頁(yè)當(dāng)前第81頁(yè)第82頁(yè)第83頁(yè)第84頁(yè)第85頁(yè)第86頁(yè)第87頁(yè)第88頁(yè)第89頁(yè)第90頁(yè)第91頁(yè)第92頁(yè)第93頁(yè)第94頁(yè)第95頁(yè)第96頁(yè)第97頁(yè)第98頁(yè)第99頁(yè)第100頁(yè)第101頁(yè)第102頁(yè)第103頁(yè)第104頁(yè)第105頁(yè)第106頁(yè)第107頁(yè)第108頁(yè)第109頁(yè)第110頁(yè)第111頁(yè)第112頁(yè)第113頁(yè)第114頁(yè)第115頁(yè)第116頁(yè)第117頁(yè)第118頁(yè)第119頁(yè)第120頁(yè)第121頁(yè)第122頁(yè)第123頁(yè)第124頁(yè)第125頁(yè)第126頁(yè)第127頁(yè)第128頁(yè)第129頁(yè)第130頁(yè)第131頁(yè)第132頁(yè)第133頁(yè)第134頁(yè)第135頁(yè)第136頁(yè)第137頁(yè)第138頁(yè)第139頁(yè)第140頁(yè)第141頁(yè)第142頁(yè)第143頁(yè)第144頁(yè)第145頁(yè)第146頁(yè)第147頁(yè)第148頁(yè)第149頁(yè)第150頁(yè)第151頁(yè)第152頁(yè)第153頁(yè)第154頁(yè)第155頁(yè)第156頁(yè)第157頁(yè)第158頁(yè)第159頁(yè)第160頁(yè)第161頁(yè)第162頁(yè)第163頁(yè)第164頁(yè)第165頁(yè)第166頁(yè)第167頁(yè)第168頁(yè)第169頁(yè)第170頁(yè)第171頁(yè)第172頁(yè)

Rev.1.01 2003.07.16 page 81 of 170

M37281MAH

–

XXXSP,M37281MFH

–

XXXSP,M37281MKH

–

XXXSP, M37281EKSP

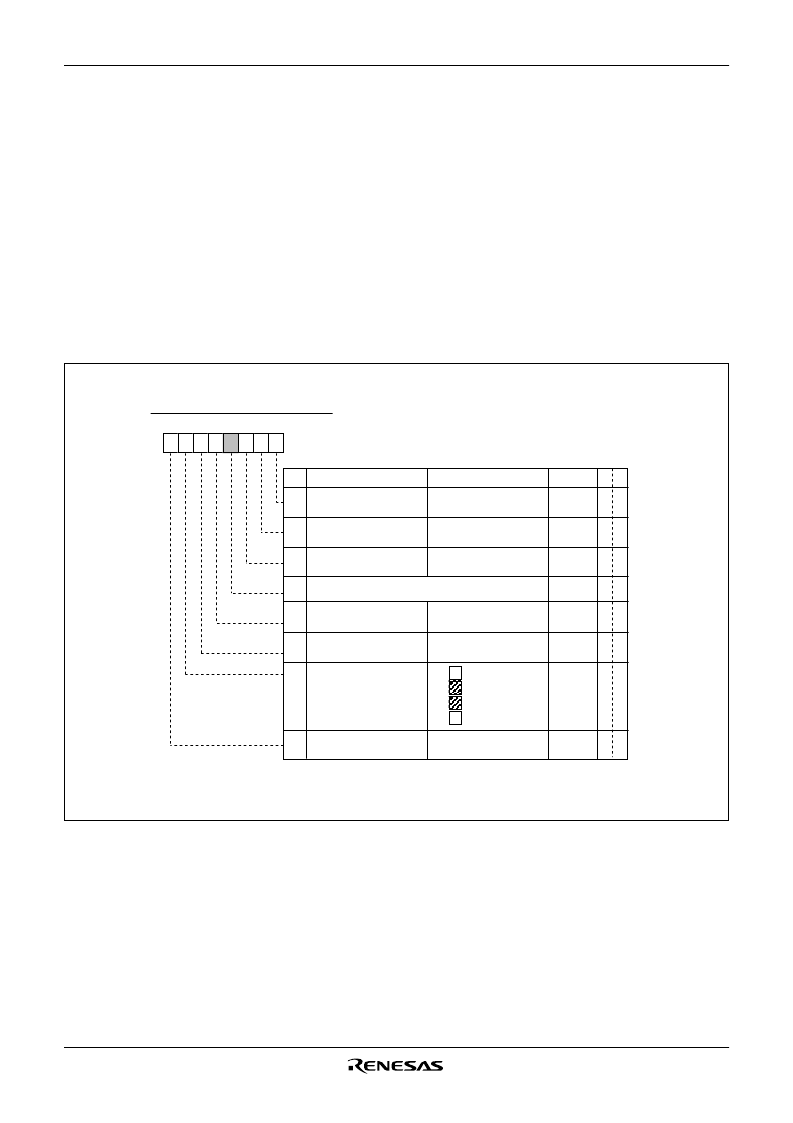

8.11.5 Field Determination Display

To display the block with vertical dot size of 1/2H, whether an even

field or an odd field is determined through differences in a synchro-

nizing signal waveform of interlacing system. The dot line 0 or 1 (re-

fer to Figure 8.11.19) corresponding to the field is displayed alter-

nately.

In the following, the field determination standard for the case where

both the horizontal sync signal and the vertical sync signal are nega-

tive-polarity inputs will be explained. A field determination is deter-

mined by detecting the time from a falling edge of the horizontal sync

signal until a falling edge of the V

SYNC

control signal (refer to Figure

Fig. 8.11.18 I/O Polarity Control Register

8.11.9) in the microcomputer and then comparing this time with the

time of the previous field. When the time is longer than the compar-

ing time, it is regarded as even field. When the time is shorter, it is

regarded as odd field.

The field determination flag changes at a rising edge of V

SYNC

con-

trol signal in the microcomputer.

The contents of this field can be read out by the field determination

flag (bit 7 of the I/O polarity control register at address 0217

16

). A dot

line is specified by bit 6 of the I/O polarity control register (refer to

Figure 8.11.19).

However, the field determination flag read out from the CPU is fixed

to

“

0

”

at even field or

“

1

”

at odd field, regardless of bit 6.

b7 b6 b5 b4 b3 b2 b1 b0

I/

O

p

o

l

a

r

i

t

y

c

o

n

t

r

o

l

r

e

g

i

s

t

e

r

(

P

C

)

[

A

d

d

r

e

s

s

0

2

1

7

1

6

]

B

N

a

m

e

Functions

A

f

t

e

r

r

e

s

e

t R W

I/

O

P

o

l

a

r

i

t

y

C

o

n

t

r

o

l

R

e

g

i

s

t

e

r

0

H

SYNC

input polarity

switch bit (PC0)

i

n

p

u

s

w

i

t

c

h

b

i

t

(

0 : Positive polarity input

1 : Negative polarity input

0

1

0 : Positive polarity input

1 : Negative polarity input

0

2

R, G, B output polarity

switch bit (PC2)

0 : Positive polarity output

1 : Negative polarity output

0

3

0

V

S

Y

N

C

t

P

p

C

o

1

l

a

)

r

i

t

y

R W

R W

R W

R

—

Note:

Refer to Fig. 8.11.19.

0 :

“

”

at even field

“

”

at odd field

1 :

“

”

at even field

“

”

at odd field

4

O

s

U

s

w

i

b

i

U

w

T

t

c

1

h

o

b

u

i

t

p

(

u

P

t

C

p

4

o

)

l

a

r

i

t

y

i

t

0 : Positive polarity output

1 : Negative polarity output

0

5

O

T

t

c

2

h

o

b

u

i

t

p

(

u

P

t

C

p

5

o

)

l

a

r

i

t

y

i

t

0 : Positive polarity output

1 : Negative polarity output

0

6

D

s

t

p

(

l

a

C

y

d

)

o

(

t

S

l

e

i

n

e

e

s

o

e

t

l

e

e

)

c

t

i

o

n

P

6

n

0

7

Field determination

flag(PC7)

0 : Even field

1 : Odd field

1

R W

R W

R W

R

—

Nothing is assigned. This bit is a write disable bit.

When this bit is read out, the value is

“

0

”

.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| M37281MFH-XXXSP | SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER with CLOSED CAPTION DECODER and ON-SCREEN DISPLAY CONTROLLER |

| M37281MKH-XXXSP | SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER with CLOSED CAPTION DECODER and ON-SCREEN DISPLAY CONTROLLER |

| M37534E4GP | SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER |

| M37534E4FP | SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER |

| M37544 | SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| M37281MFH-XXXSP | 制造商:RENESAS 制造商全稱:Renesas Technology Corp 功能描述:SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER with CLOSED CAPTION DECODER and ON-SCREEN DISPLAY CONTROLLER |

| M37281MKH-XXXSP | 制造商:RENESAS 制造商全稱:Renesas Technology Corp 功能描述:SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER with CLOSED CAPTION DECODER and ON-SCREEN DISPLAY CONTROLLER |

| M372899234 | 制造商:ITW Switches 功能描述:IN-RUSH |

| M372F3200DJ3-C | 制造商:SAMSUNG 制造商全稱:Samsung semiconductor 功能描述:32M x 72 DRAM DIMM with ECC Using 16Mx4, 4K & 8K Refresh, 3.3V |

| M372F3280DJ3-C | 制造商:SAMSUNG 制造商全稱:Samsung semiconductor 功能描述:32M x 72 DRAM DIMM with ECC Using 16Mx4, 4K & 8K Refresh, 3.3V |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。