- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄358968 > M16C30P (Renesas Technology Corp.) SINGLE-CHIP 16-BIT CMOS MICROCOMPUTER PDF資料下載

參數(shù)資料

| 型號(hào): | M16C30P |

| 廠商: | Renesas Technology Corp. |

| 英文描述: | SINGLE-CHIP 16-BIT CMOS MICROCOMPUTER |

| 中文描述: | 單片16位CMOS微機(jī) |

| 文件頁(yè)數(shù): | 24/57頁(yè) |

| 文件大?。?/td> | 583K |

| 代理商: | M16C30P |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)當(dāng)前第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)

M16C/30P Group

5. Electrical Characteristics

Rev.1.22

REJ03B0088-0122

Mar 30, 2007

Page 24 of 53

NOTES:

1.

2.

3.

Referenced to V

CC1

= V

CC2 =

2.7 to 5.5V at T

opr

=

20 to 85

°

C /

40 to 85

°

C unless otherwise specified.

The Average Output Current is the mean value within 100ms.

The total I

OL(peak)

for ports P0, P1, P2, P8_6, P8_7, P9 and P10 must be 80mA max. The total I

OL(peak)

for ports P3, P4, P5,

P6, P7 and P8_0 to P8_4 must be 80mA max. The total I

OH(peak)

for ports P0, P1, and P2 must be

40mA max. The total

I

OH(peak)

for ports P3, P4 and P5 must be

40mA max. The total I

OH(peak)

for ports P6, P7, and P8_0 to P8_4 must be

40mA

max.

The total I

OH(peak)

for ports P8_6, P8_7 and P9 must be

40mA max. Set Average Output Current to 1/2 of

peak

.

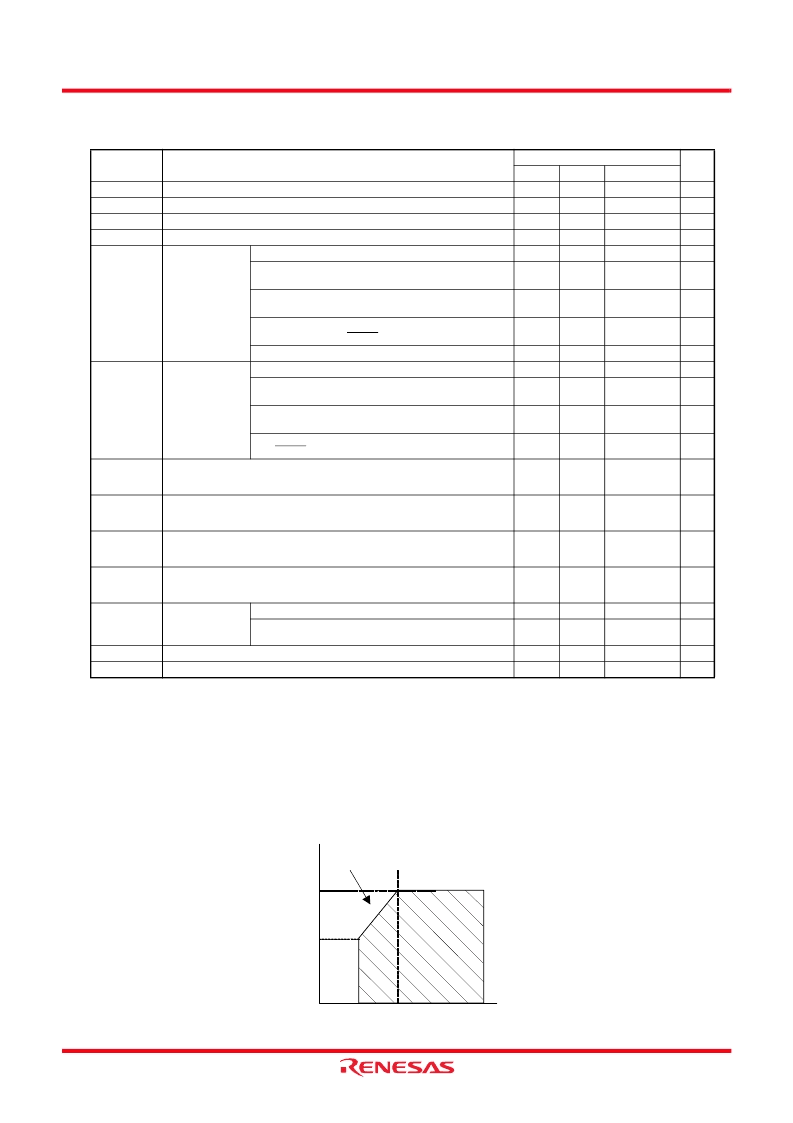

Relationship between main clock oscillation frequency, and supply voltage.

4.

Table 5.2

Recommended Operating Conditions

(1)

Symbol

Parameter

Standard

Typ.

5.0

V

CC

0

0

Unit

Min.

2.7

Max.

5.5

V

CC

AV

CC

V

SS

AV

SS

V

IH

Supply Voltage (V

CC1

=V

CC2

)

Analog Supply Voltage

Supply Voltage

Analog Supply Voltage

HIGH Input

Voltage

V

V

V

V

V

V

P3_1 to P3_7, P4_0 to P4_7, P5_0 to P5_7

0.8V

CC

0.8V

CC

V

CC

V

CC

P0_0 to P0_7, P1_0 to P1_7, P2_0 to P2_7, P3_0

(during single-chip mode)

P0_0 to P0_7, P1_0 to P1_7, P2_0 to P2_7, P3_0

(data input during memory expansion and microprocessor mode)

P6_0 to P6_7, P7_2 to P7_7, P8_0 to P8_7, P9_0 to P9_7,

P10_0 to P10_7, XIN, RESET, CNVSS, BYTE

P7_0, P7_1

0.5V

CC

V

CC

V

0.8V

CC

V

CC

V

0.8V

CC

0

0

6.5

V

V

V

V

IL

LOW Input

Voltage

P3_1 to P3_7, P4_0 to P4_7, P5_0 to P5_7

0.2V

CC

0.2V

CC

P0_0 to P0_7, P1_0 to P1_7, P2_0 to P2_7, P3_0

(during single-chip mode)

P0_0 to P0_7, P1_0 to P1_7, P2_0 to P2_7, P3_0

(data input during memory expansion and microprocessor mode)

P6_0 to P6_7, P7_0 to P7_7, P8_0 to P8_7, P9_0 to P9_7,

XIN, RESET, CNVSS, BYTE

P0_0 to P0_7, P1_0 to P1_7, P2_0 to P2_7, P3_0 to P3_7,

P4_0 to P4_7, P5_0 to P5_7, P6_0 to P6_7, P7_2 to P7_7,

P8_0 to P8_4, P8_6, P8_7, P9_0 to P9_7, P10_0 to P10_7

P0_0 to P0_7, P1_0 to P1_7, P2_0 to P2_7, P3_0 to P3_7,

P4_0 to P4_7, P5_0 to P5_7, P6_0 to P6_7, P7_2 to P7_7,

P8_0 to P8_4, P8_6, P8_7, P9_0 to P9_7, P10_0 to P10_7

P0_0 to P0_7, P1_0 to P1_7, P2_0 to P2_7, P3_0 to P3_7,

P4_0 to P4_7, P5_0 to P5_7, P6_0 to P6_7, P7_0 to P7_7,

P8_0 to P8_4, P8_6, P8_7, P9_0 to P9_7, P10_0 to P10_7

P0_0 to P0_7, P1_0 to P1_7, P2_0 to P2_7, P3_0 to P3_7,

P4_0 to P4_7, P5_0 to P5_7, P6_0 to P6_7, P7_0 to P7_7,

P8_0 to P8_4, P8_6, P8_7, P9_0 to P9_7, P10_0 to P10_7

V

CC

=3.0V to 5.5V

0

0.16V

CC

V

0

0.2V

CC

V

I

OH(peak)

HIGH Peak

Output Current

10.0

mA

I

OH(avg)

HIGH Average

Output Current

5.0

mA

I

OL(peak)

LOW Peak

Output Current

10.0

mA

I

OL(avg)

LOW Average

Output Current

5.0

mA

f(XIN)

Main Clock Input

Oscillation

Frequency

(4)

Sub-Clock Oscillation Frequency

CPU Operation Clock

0

0

16

MHz

MHz

V

CC

=2.7V to 3.0V

20×V

CC1

44

f(XCIN)

f(BCLK)

32.768

50

16

kHz

MHz

0

Main clock input oscillation frequency

16.0

0.0

f

VCC1[V] (main clock: no division)

5.5

3.0

10.0

2.7

20 x V

CC1

-44MHz

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| M2201 | 2-Wires 1 Kbit x8 Serial EEPROM |

| M22100 | 4 X 4 CROSSPOINT SWITCH WITH CONTROL MEMORY |

| M22102F1 | 5015 RR 4#12 SKT PLUG |

| M22102 | WITH CONTROL MEMORY 4 X 4 X 2 CROSSPOINT SWITCHES |

| M22102B1 | WITH CONTROL MEMORY 4 X 4 X 2 CROSSPOINT SWITCHES |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| M16C30P_07 | 制造商:RENESAS 制造商全稱:Renesas Technology Corp 功能描述:16-BIT SINGLE-CHIP MICROCOMPUTER M16C FAMILY / M16C/30 SERIES |

| M16C57 | 制造商:RENESAS 制造商全稱:Renesas Technology Corp 功能描述:RENESAS MCU |

| M16C5LD | 制造商:RENESAS 制造商全稱:Renesas Technology Corp 功能描述:RENESAS MCU |

| M16C5M | 制造商:RENESAS 制造商全稱:Renesas Technology Corp 功能描述:RENESAS MCU |

| M16C62 | 制造商:RENESAS 制造商全稱:Renesas Technology Corp 功能描述:16-BIT SINGLE-CHIP MICROCOMPUTER M16C FAMILY / M16C/60 SERIES |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。