- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄369886 > LXT9762HC LAN TRANSCEIVER|HEX|QFP|208PIN|PLASTIC PDF資料下載

參數(shù)資料

| 型號(hào): | LXT9762HC |

| 英文描述: | LAN TRANSCEIVER|HEX|QFP|208PIN|PLASTIC |

| 中文描述: | 網(wǎng)絡(luò)收發(fā)器|六角| QFP封裝| 208PIN |塑料 |

| 文件頁數(shù): | 49/68頁 |

| 文件大?。?/td> | 1177K |

| 代理商: | LXT9762HC |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁當(dāng)前第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁

Low-Power Octal PHY

—

LXT9784

Datasheet

49

3.3.1

RMII Clock

In RMII mode of operation, the master input clock (MCLK) frequency should be 50 MHz ± 50

ppm, with a duty-cycle between 35% and 65% inclusive.

3.4

SMII Applications

The SMII ports provide eight low pin-count interfaces between the LXT9784

’

s eight PHYs and an

ASIC switch, as an alternative to the RMII interface. The SMII interface is composed of two

signals per port, a global synchronization signal, and a global reference clock.

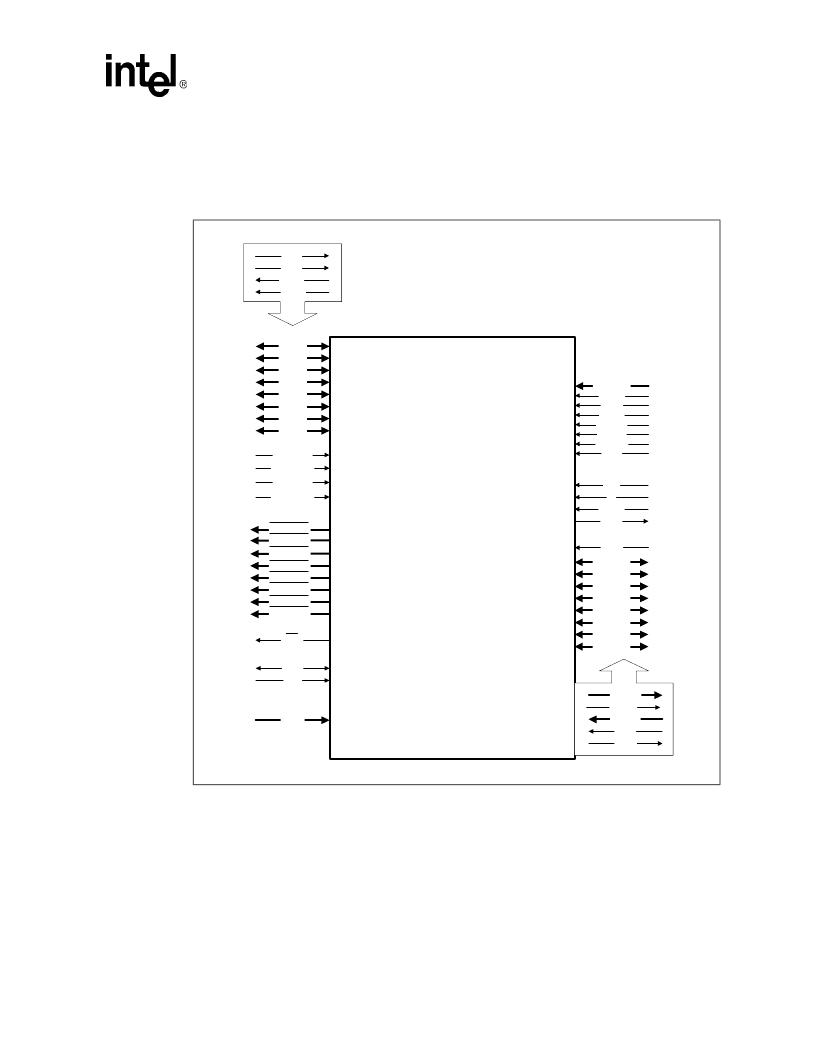

Figure 13. Typical RMII Application

LXT9784

P0_MDI

P1_MDI

P2_MDI

P3_MDI

P4_MDI

P5_MDI

P6_MDI

P7_MDI

MDI Ports

RBIAS100_0

RBIAS10_0

Analog pins

LED0_[A:C]

LED1_[A:C]

LED2_[A:C]

LED3_[A:C]

LED4_[A:C]

LED5_[A:C]

LED6_[A:C]

LED7_[A:C]

Per Port

LEDs

MODE[2:0]

RESET

MCLK

FRC34

Configuration

MDIO

MDC

MII Management

Interface

ID[1:0]

PHY ID

RMII0_[6:0]

RMII1_[6:0]

RMII2_[6:0]

RMII3_[6:0]

RMII4_[6:0]

RMII5_[6:0]

RMII6_[6:0]

RMII7_[6:0]

RMII

Interfaces

TPIP

INT

Interrupt

RBIAS100_1

RBIAS10_1

SCRMBP

MDIX

BP4B5B

FRCLNK

SYNC

TCK

TI

TEXEC

TOUT

Test Port

TPIN

TPOP

TPON

RXD[1:0]

TXD[1:0]

CRSDV

TXEN

RXER

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| LXT9781 | Interface IC |

| LXT9781BC | LAN TRANSCEIVER|OCTAL|BGA|272PIN|PLASTIC |

| LXT9781HC | LAN TRANSCEIVER|OCTAL|QFP|208PIN|PLASTIC |

| LXT9782 | Interface IC |

| LXT9782BC | LAN TRANSCEIVER|OCTAL|BGA|272PIN|PLASTIC |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| LXT9763 | 制造商:INTEL 制造商全稱:Intel Corporation 功能描述:Fast Ethernet 10/100 Hex Transceiver with Full MII |

| LXT9763HC | 制造商:LEVEL_ONE 功能描述: |

| LXT9763HC-B2 | 制造商:Intel 功能描述: |

| LXT9763HC-C4 | 制造商:Intel 功能描述: |

| LXT9781 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Interface IC |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。