- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄377798 > LXT381BE (INTEL CORP) Octal E1 Line Interface Unit PDF資料下載

參數(shù)資料

| 型號: | LXT381BE |

| 廠商: | INTEL CORP |

| 元件分類: | 數(shù)字傳輸電路 |

| 英文描述: | Octal E1 Line Interface Unit |

| 中文描述: | DATACOM, PCM TRANSCEIVER, PBGA160 |

| 封裝: | PLASTIC, BGA-160 |

| 文件頁數(shù): | 22/36頁 |

| 文件大小: | 218K |

| 代理商: | LXT381BE |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁當(dāng)前第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁

LXT381

—

Octal E1 Line Interface

22

Datasheet

28

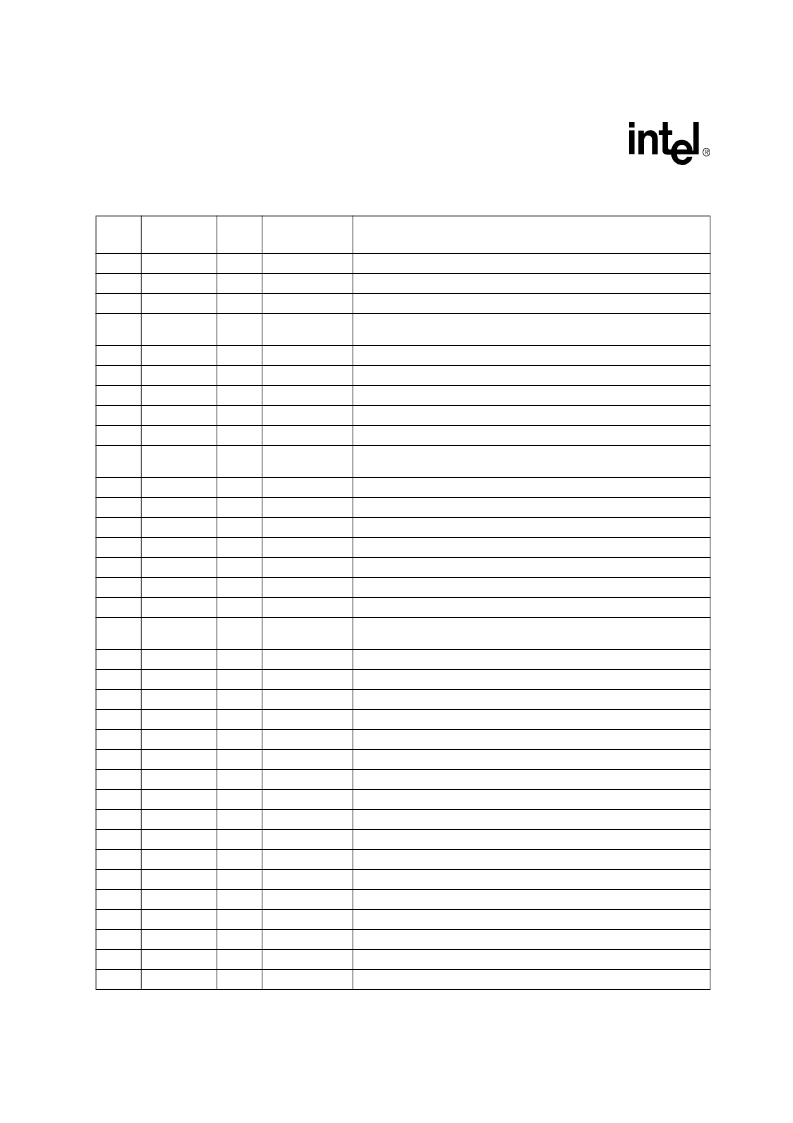

RCLK0

O

RCLK0

29

RPOS0

O

RPOS0

30

RNEG0

O

RNEG0

31

N/A

-

HIZB0

HIZB0 controls the RPOS0, RNEG0 and RCLK0 pins. Setting HIZB0 to

“

1

”

enables output on the pins. Setting HIZB0 to

“

0

”

tristates the pins.

32

LOS0

O

LOS0

33

-

-

RESERVED1

34

LOS3

O

LOS3

35

RNEG3

O

RNEG3

36

RPOS3

O

RPOS3

37

N/A

-

HIZB3

HIZB3 controls the RPOS3, RNEG3 and RCLK3 pins. Setting HIZB3 to

“

1

”

enables output on the pins. Setting HIZB3 to

“

0

”

tristates the pins.

38

RCLK3

O

RCLK3

39

TNEG3

I

TNEG3

40

TPOS3

I

TPOS3

41

TCLK3

I

TCLK3

42

LOS2

O

LOS2

43

RNEG2

O

RNEG2

44

RPOS2

O

RPOS2

45

N/A

-

HIZB2

HIZB2 controls the RPOS2, RNEG2 and RCLK2 pins. Setting HIZB2 to

“

1

”

enables output on the pins. Setting HIZB2 to

“

0

”

tristates the pins.

46

RCLK2

O

RCLK2

47

TNEG2

I

TNEG2

48

TPOS2

I

TPOS2

49

TCLK2

I

TCLK2

50

-

-

RESERVED2

51

-

-

RESERVED3

52

-

-

RESERVED4

53

-

-

RESERVED5

54

-

-

RESERVED6

55

-

-

RESERVED7

56

-

-

RESERVED8

57

-

-

RESERVED9

58

TCLK5

I

TCLK5

59

TPOS5

I

TPOS5

60

TNEG5

I

TNEG5

61

RCLK5

O

RCLK5

62

RPOS5

O

RPOS5

Table 4. Boundary Scan Register (BSR) (Continued)

Bit #

Pin

Signal

I/O

Type

Bit

Symbol

Comments

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| LXT381LE | Octal E1 Line Interface Unit |

| LXT381 | Octal E1 Line Interface Unit |

| LXT386 | QUAD T1/E1/J1 Transceiver |

| LXT400 | All Rate Extended Range Switched 56/DDS Transceiver |

| LXT441 | Switched 56/DDS Integrated DSU/CSU |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| LXT381LE | 制造商:INTEL 制造商全稱:Intel Corporation 功能描述:Octal E1 Line Interface Unit |

| LXT384/LXT386/LXT388 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:LXT384/LXT386/LXT388 - LXT384/6/8 Twisted Pair Interface Without Component Changes |

| LXT384BE | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Telecomm/Datacomm |

| LXT384LE | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Telecomm/Datacomm |

| LXT386 | 制造商:INTEL 制造商全稱:Intel Corporation 功能描述:QUAD T1/E1/J1 Transceiver |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。