- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄369885 > LXT362PE PCM TRANSCEIVER|SINGLE|T-1(DS1)|CMOS|LDCC|28PIN|PLASTIC PDF資料下載

參數(shù)資料

| 型號(hào): | LXT362PE |

| 英文描述: | PCM TRANSCEIVER|SINGLE|T-1(DS1)|CMOS|LDCC|28PIN|PLASTIC |

| 中文描述: | 的PCM收發(fā)器|單|的T 1(DS1的)|的CMOS | LDCC | 28腳|塑料 |

| 文件頁(yè)數(shù): | 11/52頁(yè) |

| 文件大小: | 1187K |

| 代理商: | LXT362PE |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)當(dāng)前第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)

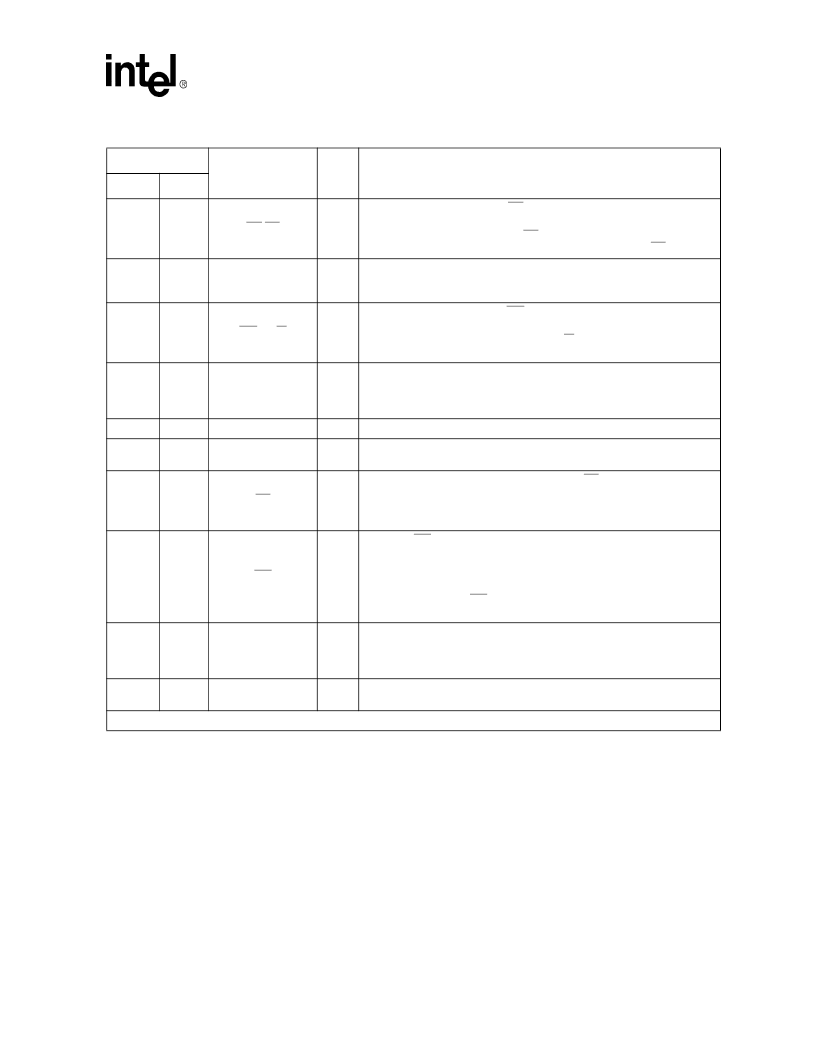

Integrated T1/E1 LH/SH Transceiver for DS1/DSX-1 or PRI Applications

—

LXT361

Datasheet

11

9

7

RD/DS

DI

Read.

On an Intel bus, driving RD Low commands a LXT361 register read

operation.

Data Strobe.

On a Motorola bus, DS goes Low when data is being driven

on the address/data bus. Data is valid on the rising edge of DS.

10

11

9

10

AD6

AD7

DI/O

Address/Data Bus 6 and 7.

Used with AD0 - AD5 to form the address/

data bus. Conforms to Intel and Motorola multiplexed address/data bus

specifications.

12

13

WR / R/W

DI

Write.

On an Intel bus, driving WR Low commands a LXT361 register write

operation.

Read/Write.

On a Motorola bus, driving R/W High commands a LXT361

register read operation; driving it Low commands a write operation.

13

16

15

19

TTIP

TRING

AO

Transmit Tip and Ring

. Differential driver output pair designed to drive a

50 - 200

load. The transformer and line matching resistors should be

selected to give the desired pulse height and return loss performance. See

“

Application Information

”

on page 32

.

14

16

TGND

-

Ground

return for the transmit driver power supply TVCC.

15

18

TVCC

-

+5 VDC Power Supply

for the transmit drivers. TVCC must not vary from

VCC by more than ± 0.3 V.

17

20

CS

DI

Chip Select.

During a read or write operation, CS must remain Low. See

Figure 16

and

Figure 17

for timing requirements.

In the case of a single processor controlling several chips, this line is used

to select a specific transceiver.

18

21

INT

DO

Interrupt.

INT goes Low to flag the host when LOS, AIS, NLOOP, QRSS,

DFMS or DFMO bits changes state, or when an elastic store overflow or

underflow occurs. To identify the specific interrupt, read the Performance

Status Register (PSR). To clear or mask an interrupt, write a one to the

appropriate bit in the Interrupt Clear Register (ICR). To re-enable the

interrupt, write a zero. INT is an

open drain output

that must be

connected to VCC through a pull-up resistor.

19

20

24

25

RTIP

RRING

AI

Receive Tip and Ring

. The Alternate Mark Inversion (AMI) signal received

from the line is applied at these pins. A 1:1 transformer is required. Data

and clock recovered from RTIP/RRING are output on the RPOS/RNEG (or

RDATA in

Unipolar mode

), and RCLK pins.

21

27

VCC

-

+5 VDC Power Supply

for all circuits except the transmit drivers. Transmit

drivers are supplied by TVCC.

Table 3. LXT361 Signal Descriptions (Continued)

Pin #

Symbol

I/O

1

Description

PLCC

QFP

1. DI = Digital Input; DO = Digital Output; DI/O = Digital Input/Output; AI = Analog Input; AO = Analog Output.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| LXT362QE | PCM TRANSCEIVER|SINGLE|T-1(DS1)|CMOS|QFP|44PIN|PLASTIC |

| LXT363LE | PCM TRANSCEIVER|SINGLE|T-1(DS1)|CMOS|QFP|44PIN|PLASTIC |

| LXT363PE | PCM TRANSCEIVER|SINGLE|T-1(DS1)|CMOS|LDCC|28PIN|PLASTIC |

| LXT363QE | PCM TRANSCEIVER|SINGLE|T-1(DS1)|CMOS|QFP|44PIN|PLASTIC |

| LXT360LE | PCM TRANSCEIVER|SINGLE|CEPT PCM-30/E-1|CMOS|QFP|44PIN|PLASTIC |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| LXT362QE | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:PCM TRANSCEIVER|SINGLE|T-1(DS1)|CMOS|QFP|44PIN|PLASTIC |

| LXT363LE | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:PCM TRANSCEIVER|SINGLE|T-1(DS1)|CMOS|QFP|44PIN|PLASTIC |

| LXT363PE | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:PCM TRANSCEIVER|SINGLE|T-1(DS1)|CMOS|LDCC|28PIN|PLASTIC |

| LXT363QE | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:PCM TRANSCEIVER|SINGLE|T-1(DS1)|CMOS|QFP|44PIN|PLASTIC |

| LXT36X/35X | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:LXT36x/35x - LXT36x/35x Master Clock Requirements |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。