- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄361036 > LM98501CCVBH (NATIONAL SEMICONDUCTOR CORP) 10-Bit, 27 MSPS Camera Signal Processor PDF資料下載

參數(shù)資料

| 型號(hào): | LM98501CCVBH |

| 廠商: | NATIONAL SEMICONDUCTOR CORP |

| 元件分類: | 消費(fèi)家電 |

| 英文描述: | 10-Bit, 27 MSPS Camera Signal Processor |

| 中文描述: | SPECIALTY CONSUMER CIRCUIT, PQFP48 |

| 封裝: | LQFP-48 |

| 文件頁(yè)數(shù): | 18/24頁(yè) |

| 文件大小: | 490K |

| 代理商: | LM98501CCVBH |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)當(dāng)前第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)

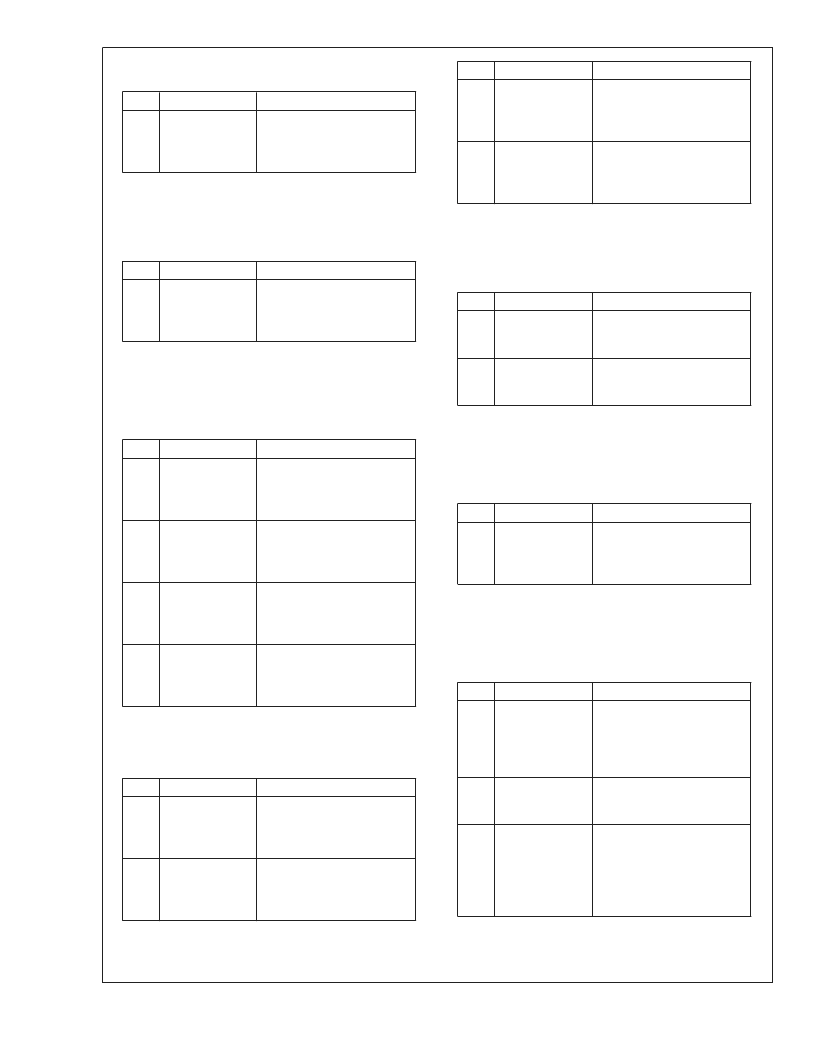

Register Data

(Continued)

Bit

[7:0]

Bit Symbol

Signed Analog

Offset

Description

Digital representation of the

analog offset to be applied to

the input of the PGA. See

“Analog Offset” on page 15.

Register Name Analog Offset 3

Address

Type

Reset Value

7 Hex

Read/Write

0000 0000 Binary

Bit

[7:0]

Bit Symbol

Signed Analog

Offset

Description

Digital representation of the

analog offset to be applied to

the input of the PGA. See

“Analog Offset” on page 15.

COLOR FILTER ARRAY REGISTERS

Register Name Color Filter Array Configuration 0

Address

8 Hex

Type

Read/Write

Reset Value

0000 0000 Binary

Bit

[7:6]

Bit Symbol

Line0:Pixel3

Gain/Offset

Description

2 LSB’s of register

addresses where the gain

and offset for pixel 3 of the

CFA pattern are stored.

2 LSB’s of register

addresses where the gain

and offset for pixel 2 of the

CFA pattern are stored.

2 LSB’s of register

addresses where the gain

and offset for pixel 1 of the

CFA pattern are stored.

2 LSB’s of register

addresses where the gain

and offset for pixel 0 of the

CFA pattern are stored.

[5:4]

Line0:Pixel2

Gain/Offset

[3:2]

Line0:Pixel1

Gain/Offset

[1:0]

Line0:Pixel0

Gain/Offset

Register Name Color Filter Array Configuration 1

Address

9 Hex

Type

Read/Write

Reset Value

0000 0000 Binary

Bit

[7:6]

Bit Symbol

Line1:Pixel3

Gain/Offset

Description

2 LSB’s of register

addresses where the gain

and offset for pixel 3 of the

CFA pattern are stored.

2 LSB’s of register

addresses where the gain

and offset for pixel 2 of the

CFA pattern are stored.

[5:4]

Line1:Pixel2

Gain/Offset

Bit

[3:2]

Bit Symbol

Line1:Pixel1

Gain/Offset

Description

2 LSB’s of register

addresses where the gain

and offset for pixel 1 of the

CFA pattern are stored.

2 LSB’s of register

addresses where the gain

and offset for pixel 0 of the

CFA pattern are stored.

[1:0]

Line1:Pixel0

Gain/Offset

Register Name Color Filter Array Definition

Address

A Hex

Type

Read/Write

Reset Value

XXXX 0000 Binary

Bit

[3:2]

Bit Symbol

Line 1 Pixels

Description

Number of pixels in CFA

pattern defined in CFA line

1.

Number of pixels in CFA

pattern defined in CFA line

0.

[2:1]

Line 0 Pixels

OUTPUT BLACK LEVEL REGISTER

Register Name Output Black Level

Address

B Hex

Type

Read/Write

Reset Value

0001 0000 Binary

Bit

[7:0]

Bit Symbol

Black Level

Description

0–256 output black level

digital code value. (see

“Output Black Level” on

page 15)

SOFTWARE CONTROL REGISTERS

Register Name Software Control 0 (Customer)

Address

C Hex

Type

Read/Write

Reset Value

0100 1110 Binary

Bit

[7]

Bit Symbol

Offset Output

Enable

Description

Directs the offset error

calculated by the digital

black level correction loop to

the 10 digital output data

pins.

Enables the serial interface

output for reading register

values.

Offset integration factor

selection:

00 No Scaling

01 Divide-by-4

10 Divide-by-8

11 Divide-by-16

[6]

Serial Output

Enable

[5:4]

Offset

Integration

L

www.national.com

18

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| LM98501 | 10-Bit, 27 MSPS Camera Signal Processor |

| LMC555CBPEVAL | CMOS Timer |

| LMC555CN | CMOS Timer |

| LMC555 | CMOS Timer |

| LMC555CM | CMOS Timer |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| LM98501VBH WAF | 制造商:Texas Instruments 功能描述: |

| LM98502A WAF | 制造商:Texas Instruments 功能描述: |

| LM98503 | 制造商:NSC 制造商全稱:National Semiconductor 功能描述:10-Bit, 18 MSPS Camera Signal Processor |

| LM98503CCVV | 制造商:NSC 制造商全稱:National Semiconductor 功能描述:10-Bit, 18 MSPS Camera Signal Processor |

| LM98510CCMT | 制造商:Rochester Electronics LLC 功能描述: 制造商:Texas Instruments 功能描述: |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。