- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄360998 > ISP1161 (NXP Semiconductors N.V.) Full-speed Universal Serial Bus single-chip host and device controller PDF資料下載

參數(shù)資料

| 型號(hào): | ISP1161 |

| 廠商: | NXP Semiconductors N.V. |

| 英文描述: | Full-speed Universal Serial Bus single-chip host and device controller |

| 中文描述: | 全速通用串行總線的單芯片主機(jī)和設(shè)備控制器 |

| 文件頁數(shù): | 29/127頁 |

| 文件大小: | 2762K |

| 代理商: | ISP1161 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁當(dāng)前第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁第113頁第114頁第115頁第116頁第117頁第118頁第119頁第120頁第121頁第122頁第123頁第124頁第125頁第126頁第127頁

Philips Semiconductors

ISP1161

Full-speed USB single-chip host and device controller

Product data

Rev. 01 — 3 July 2001

29 of 130

9397 750 08313

Philips Electronics N.V. 2001. All rights reserved.

The data transfer can be done via PIO mode or DMA mode. The data transfer rate

can go up to 15 Mbyte/s. In DMA operation, single-cycle or multi-cycle burst modes

are supported. For the multi-cycle burst mode, 1, 4, or 8 cycles per burst is supported

for ISP1161.

9.4.2

Data organization

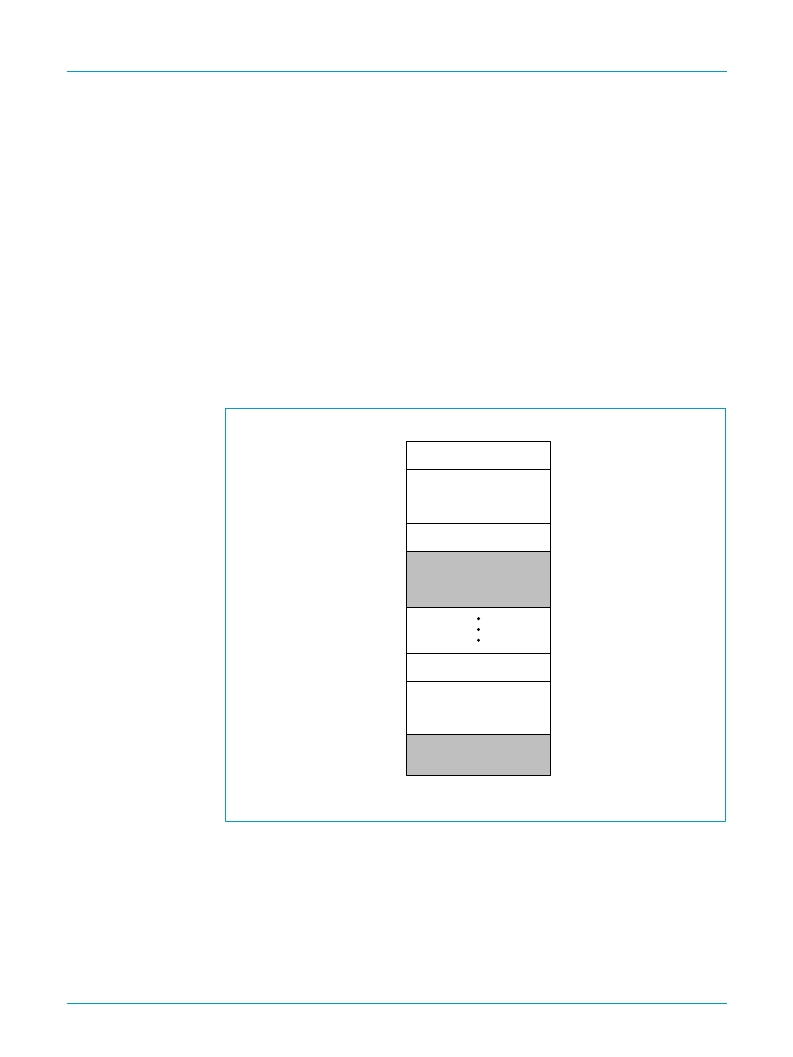

PTD data is used for every data transfer between a microprocessor and the USB bus,

and the PTD data resides in the buffer RAM. For an OUT or SETUP transfer, the

payload data is placed just after the PTD, after which the next PTD is placed. For an

IN transfer, some RAM space is reserved for receiving a number of bytes that is equal

to the total bytes of the transfer. After this, the next PTD and its payload data are

placed (see

Figure 27

).

Remark:

The PTD is defined for both ATL and ITL type data transfer. For ITL, the

PTD data should be put into ITL buffer RAM, the ISP1161 takes care of the

Ping-Pong action for the ITL buffer RAM access.

The PTD data (PTD header and its payload data) is a structure of DWORD (double-

word or 4-byte) alignment. This means that the memory address is organized in steps

of 4 bytes. Therefore, the first byte of every PTD and the first byte of every payload

data are located at an address which is a multiple of 4.

Figure 28

illustrates an

example in which the first payload data is 14 bytes long, meaning that the last byte of

the payload data is at the location 15H. The next addresses (16H and 17H) are not

multiples of 4. Therefore, the first byte of the next PTD will be located at the next

multiple-of-four address, 18H.

Fig 27. Buffer RAM data organization.

MGT952

PTD of OUT transfer

RAM buffer

payload data of OUT transfer

PTD of IN transfer

empty space for IN total data

PTD of OUT transfer

payload data of OUT transfer

top

bottom

000H

7FFH

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| ISP1161A1 | Universal Serial Bus single-chip host and device controller |

| ISP1161A1BD | Universal Serial Bus single-chip host and device controller |

| ISP1161A1BM | Universal Serial Bus single-chip host and device controller |

| ISP1161BD | Full-speed Universal Serial Bus single-chip host and device controller |

| ISP1161BM | Full-speed Universal Serial Bus single-chip host and device controller |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| ISP1161A | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:Full-speed Universal Serial Bus single-chip host and device controller |

| ISP1161A1 | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:Universal Serial Bus single-chip host and device controller |

| ISP1161A1BD | 功能描述:IC USB HOST/DEVICE CTRLR 64-LQFP RoHS:是 類別:集成電路 (IC) >> 接口 - 控制器 系列:- 標(biāo)準(zhǔn)包裝:4,900 系列:- 控制器類型:USB 2.0 控制器 接口:串行 電源電壓:3 V ~ 3.6 V 電流 - 電源:135mA 工作溫度:0°C ~ 70°C 安裝類型:表面貼裝 封裝/外殼:36-VFQFN 裸露焊盤 供應(yīng)商設(shè)備封裝:36-QFN(6x6) 包裝:* 其它名稱:Q6396337A |

| ISP1161A1BD,118 | 功能描述:USB 接口集成電路 USB1.1 HOST &DEVICE RoHS:否 制造商:Cypress Semiconductor 產(chǎn)品:USB 2.0 數(shù)據(jù)速率: 接口類型:SPI 工作電源電壓:3.15 V to 3.45 V 工作電源電流: 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:WLCSP-20 |

| ISP1161A1BD,151 | 功能描述:USB 接口集成電路 USB1.1 HOST &DEVICE RoHS:否 制造商:Cypress Semiconductor 產(chǎn)品:USB 2.0 數(shù)據(jù)速率: 接口類型:SPI 工作電源電壓:3.15 V to 3.45 V 工作電源電流: 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:WLCSP-20 |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。