- 您現(xiàn)在的位置:買賣IC網 > PDF目錄296206 > IDT72V3640L39268BBGI (INTEGRATED DEVICE TECHNOLOGY INC) 1K X 36 OTHER FIFO, 5 ns, PBGA144 PDF資料下載

參數資料

| 型號: | IDT72V3640L39268BBGI |

| 廠商: | INTEGRATED DEVICE TECHNOLOGY INC |

| 元件分類: | FIFO |

| 英文描述: | 1K X 36 OTHER FIFO, 5 ns, PBGA144 |

| 封裝: | 13 X 13 MM, 1 MM PITCH, GREEN, PLASTIC, BGA-144 |

| 文件頁數: | 28/46頁 |

| 文件大小: | 453K |

| 代理商: | IDT72V3640L39268BBGI |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁當前第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁

34

COMMERCIAL AND INDUSTRIAL

TEMPERATURE RANGES

IDT72V3640/50/60/70/80/90 3.3V HIGH DENSITY SUPERSYNC IITM 36-BIT FIFO

1,024 x 36, 2,048 x 36, 4,096 x 36, 8,192 x 36, 16,384 x 36 and 32,768 x 36

NOVEMBER 2, 2005

NOTES:

1. m =

PAF offset.

2. D = maximum FIFO depth.

In IDT Standard mode: D = 1,024 for the IDT72V3640, 2,048 for the IDT72V3650, 4,096 for the IDT72V3660 and 8,192 for the IDT72V3670, 16,384 for the IDT72V3680 and 32,768

for the IDT72V3690.

In FWFT mode: D = 1,025 for the IDT72V3640, 2,049 for the IDT72V3650, 4,097 for the IDT72V3660, 8,193 for the IDT72V3670, 16,385 for the IDT72V3680 and 32,769 for the

IDT72V3690.

3. tSKEW2 is the minimum time between a rising RCLK edge and a rising WCLK edge to guarantee that

PAF will go HIGH (after one WCLK cycle plus tPAFS). If the time between the

rising edge of RCLK and the rising edge of WCLK is less than tSKEW2, then the

PAF deassertion time may be delayed one extra WCLK cycle.

4.

PAF is asserted and updated on the rising edge of WCLK only.

5. Select this mode by setting PFM HIGH during Master Reset.

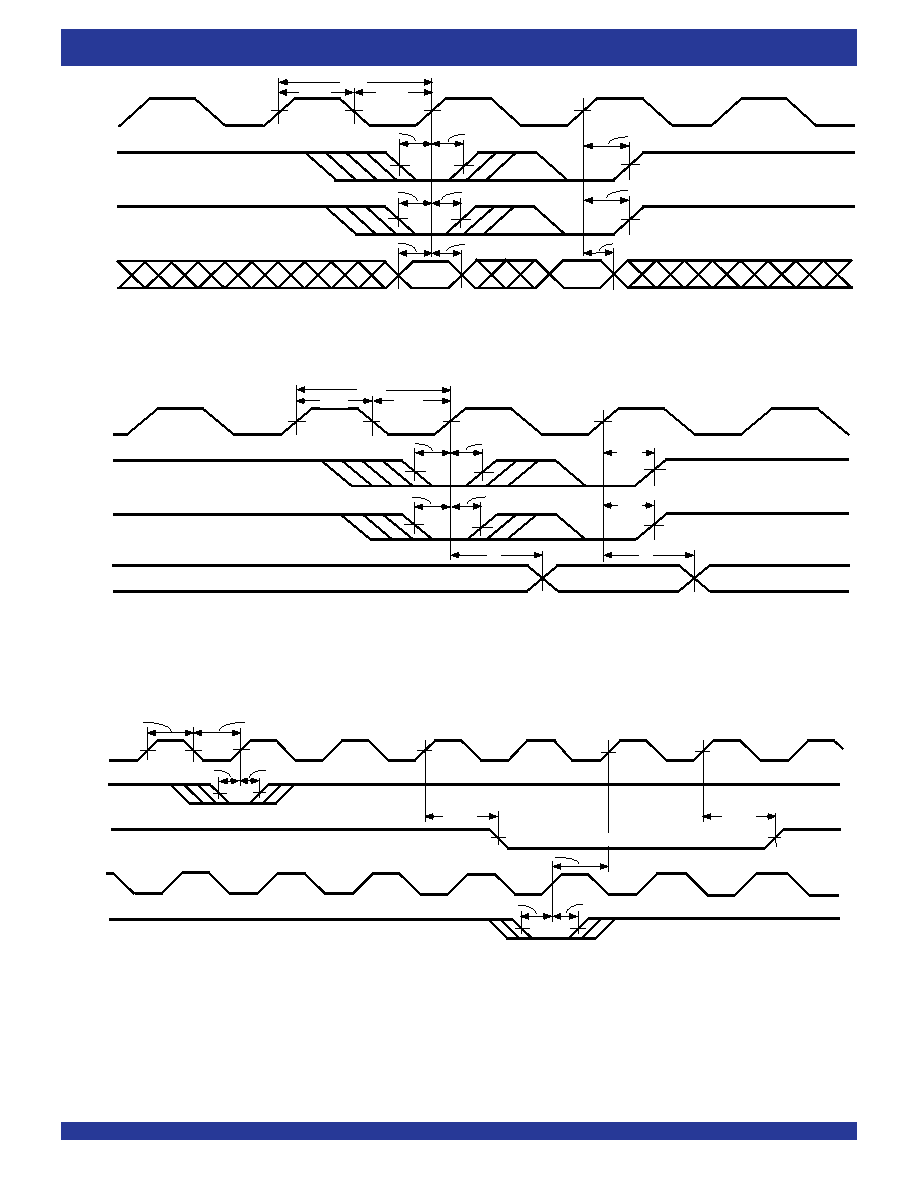

WCLK

WEN

PAF

RCLK

(3)

tPAFS

REN

4667 drw23

D - (m+1) words in FIFO(2)

D - m words in FIFO(2)

1

2

12

D-(m+1) words

in FIFO(2)

tPAFS

tENH

tENS

tSKEW2

tENH

tENS

tCLKL

RCLK

LD

REN

Q0 - Qn

tLDH

tLDS

tENS

DATA IN OUTPUT REGISTER

PAE OFFSET

PAF OFFSET

tENH

tLDH

4667 drw22

t CLK

tA

tCLKH

tCLKL

WCLK

LD

WEN

D0 - Dn

4667 drw21

tLDS

tENS

PAE

OFFSET

PAF

OFFSET

tDS

tDH

tLDH

tENH

tCLK

tLDH

tENH

tDH

tCLKH

tCLKL

Figure 18. Synchronous Programmable Almost-Full Flag Timing (IDT Standard and FWFT Modes)

NOTES:

1. OE = LOW.

2. The timing diagram illustrates reading of offset registers with an output bus width of 36 bits.

Figure 17. Parallel Read of Programmable Flag Registers (IDT Standard and FWFT Modes)

Figure 16. Parallel Loading of Programmable Flag Registers (IDT Standard and FWFT Modes)

NOTE:

1. This timing diagram illustrates programming with an input bus width of 36 bits.

相關PDF資料 |

PDF描述 |

|---|---|

| IDT79R4600-133MD | 64-BIT, 133 MHz, RISC PROCESSOR, PQFP208 |

| IDT79RV4400SC-67GL447 | 64-BIT, 67 MHz, RISC PROCESSOR, CPGA447 |

| IDT79RV4400SC-100GL447 | 64-BIT, 100 MHz, RISC PROCESSOR, CPGA447 |

| IDT7M7004S75CH | 128K X 8 EEPROM 5V MODULE, 75 ns, CPGA66 |

| IFD010P2SAXXXXX | 5 Mbps, IDE COMPATIBLE, FLASH MEMORY DRIVE CONTROLLER, XMA68 |

相關代理商/技術參數 |

參數描述 |

|---|---|

| IDT72V3640L6BB | 功能描述:IC FIFO SS 1024X36 6NS 144-BGA RoHS:否 類別:集成電路 (IC) >> 邏輯 - FIFO 系列:72V 標準包裝:90 系列:7200 功能:同步 存儲容量:288K(16K x 18) 數據速率:100MHz 訪問時間:10ns 電源電壓:4.5 V ~ 5.5 V 工作溫度:0°C ~ 70°C 安裝類型:表面貼裝 封裝/外殼:64-LQFP 供應商設備封裝:64-TQFP(14x14) 包裝:托盤 其它名稱:72271LA10PF |

| IDT72V3640L6BB8 | 功能描述:IC FIFO SS 1024X36 6NS 144-BGA RoHS:否 類別:集成電路 (IC) >> 邏輯 - FIFO 系列:72V 標準包裝:90 系列:7200 功能:同步 存儲容量:288K(16K x 18) 數據速率:100MHz 訪問時間:10ns 電源電壓:4.5 V ~ 5.5 V 工作溫度:0°C ~ 70°C 安裝類型:表面貼裝 封裝/外殼:64-LQFP 供應商設備封裝:64-TQFP(14x14) 包裝:托盤 其它名稱:72271LA10PF |

| IDT72V3640L6BBG | 制造商:Integrated Device Technology Inc 功能描述:FIFO Mem Sync Dual Depth/Width Uni-Dir 1K x 36 144-Pin BGA |

| IDT72V3640L6PF | 功能描述:IC FIFO SS 1024X36 6NS 128-TQFP RoHS:否 類別:集成電路 (IC) >> 邏輯 - FIFO 系列:72V 標準包裝:90 系列:7200 功能:同步 存儲容量:288K(16K x 18) 數據速率:100MHz 訪問時間:10ns 電源電壓:4.5 V ~ 5.5 V 工作溫度:0°C ~ 70°C 安裝類型:表面貼裝 封裝/外殼:64-LQFP 供應商設備封裝:64-TQFP(14x14) 包裝:托盤 其它名稱:72271LA10PF |

| IDT72V3640L6PF8 | 功能描述:IC FIFO SS 1024X36 6NS 128-TQFP RoHS:否 類別:集成電路 (IC) >> 邏輯 - FIFO 系列:72V 標準包裝:90 系列:7200 功能:同步 存儲容量:288K(16K x 18) 數據速率:100MHz 訪問時間:10ns 電源電壓:4.5 V ~ 5.5 V 工作溫度:0°C ~ 70°C 安裝類型:表面貼裝 封裝/外殼:64-LQFP 供應商設備封裝:64-TQFP(14x14) 包裝:托盤 其它名稱:72271LA10PF |

發(fā)布緊急采購,3分鐘左右您將得到回復。