- 您現(xiàn)在的位置:買賣IC網 > PDF目錄67711 > IDT49C465PQF8 (INTEGRATED DEVICE TECHNOLOGY INC) 49C SERIES, 32-BIT ERROR DETECT AND CORRECT CKT, PQFP144 PDF資料下載

參數(shù)資料

| 型號: | IDT49C465PQF8 |

| 廠商: | INTEGRATED DEVICE TECHNOLOGY INC |

| 元件分類: | 算術邏輯單元 |

| 英文描述: | 49C SERIES, 32-BIT ERROR DETECT AND CORRECT CKT, PQFP144 |

| 封裝: | PLASTIC, QFP-144 |

| 文件頁數(shù): | 6/39頁 |

| 文件大?。?/td> | 299K |

| 代理商: | IDT49C465PQF8 |

第1頁第2頁第3頁第4頁第5頁當前第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁

14

COMMERCIAL TEMPERATURE RANGE

IDT49C465/A

32-BIT FLOW-THRU ERROR DETECTION AND CORRECTION UNIT

64-BIT DATA WORD CONFIGURATION

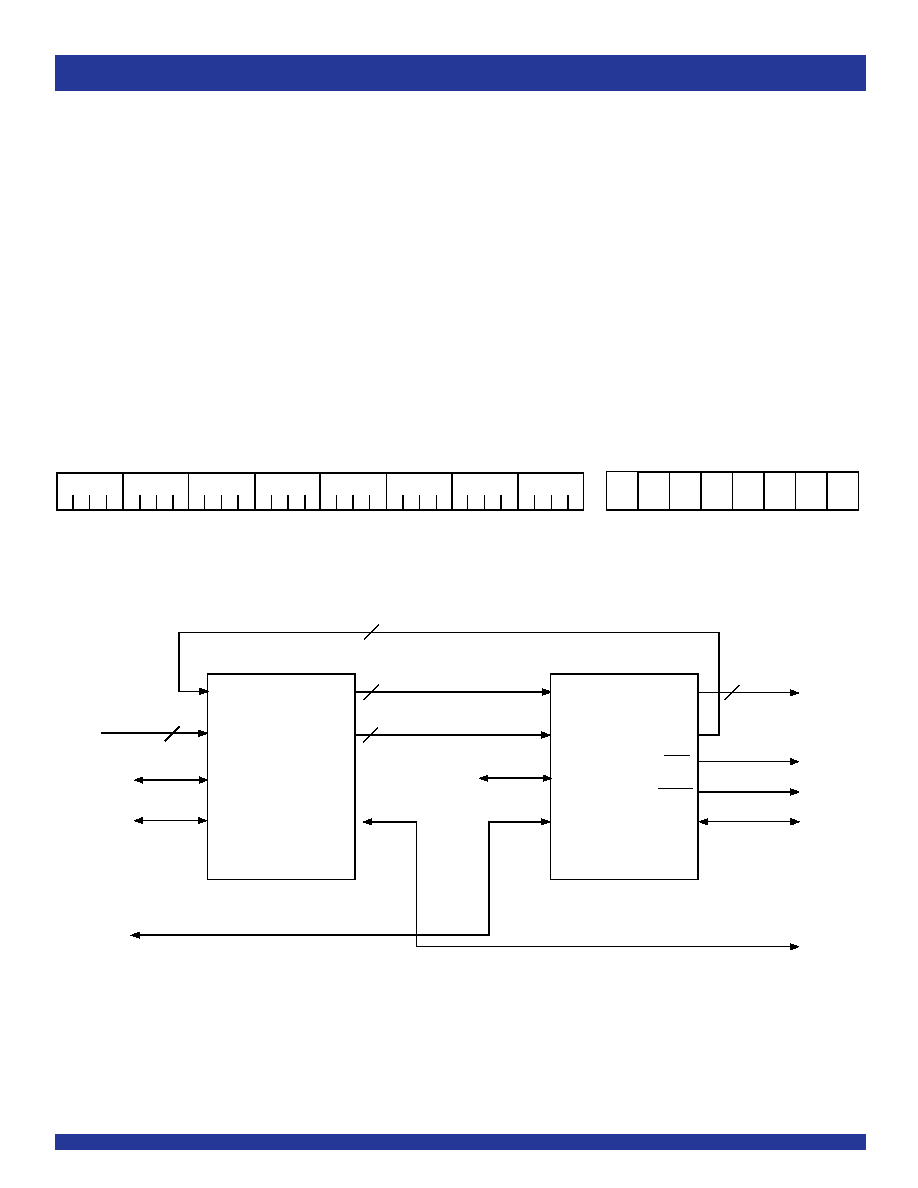

Two IDT49C465 EDC units, connected as shown below, provide all

the logic needed for single-bit error correction, and double-bit error

detection, of a 64-bit data field. The “Slice Identification” table gives the

CODE ID 1, 0 values needed for distinguishing the upper 32 bits from the

lower 32 bits. Final generated Checkbits, ERR and MERR (indicates

multiple errors) signals come from the upper slice, the IC with CODE ID

1, 0 = 11. Control signals not shown are connected to both units in

parallel.

Data-In bits 0 through 31 are connected to the same numbered inputs

of the EDC with CODE ID 1, 0 = 10 while Data-In bits 32 through 63 are

connected to data inputs 0 to 31, respectively, for the EDC unit with

CODE ID 1, 0 = 11.

The 72-bit data format of data and checkbits is indicated below.

Correction of single-bit errors in the 64-bit configuration requires a

simultaneous exchange of partial checkbits and partial syndrome bits

between the upper and lower units.

Syndrome bits are generated by an exclusive-OR of the generated

checkbits with the checkbits read from memory. For example, Sn is the

XOR of checkbits from those read with those generated. During Data

Correction, the syndrome bits are used to complement (correct) single-

bit errors in the data bits. For double or multiple-bit error detection, the

data available as output by the Pipeline Latch is not defined.

Critical AC performance data is provided in the table “Key AC

Calculations”, which illustrates the delays that are critical to 64-bit

cascaded performance. As indicated, a summation of propagation

delays is required when cascading these units.

64-BIT DATA FORMAT

64-BIT HARDWARE CONFIGURATION

C6

C5

C4

C2

C1

C3

C0

C7

CHE CKB ITS

31

24 23

16 15

8 7

0

32

39

40

47

55

56

63

48

BYTE 3

BYTE 2

BYTE 1

BYTE 0

DATA

BYTE 7

BYTE 5

BYTE 4

PC B I0-7

P0-3

SD 0-31

CBO 0-7

SYO 0-7

IDT49C 465

CHEC KBITS-IN

SYS TEM D ATA 0-31

LO W E R ED C

(CO D E ID 1,0 = 10)

PAR TIA L-C HEC KBITS

(G EN ER ATE O N LY)

PAR TIA L-S YND R O M E

(DETE CT/CO RR EC T)

8

SYS TEM D A TA 32-63

PC B I0-7

CBI0-7

P0-3

SD 0-31

CBO 0-7

SYO 0-7

ID T49C 465

MER R

ER R

MD 0-31

UPP ER ED C

(CO DE ID 1,0 = 11)

MEM O RY DATA 32-63

MEM O RY DATA 0-31

(D ETECT AND CORRECT)

FINA L C HEC KBITS

(G EN ERATE ON LY)

8

PARTIAL-C HEC KBITS (C OR R EC T O NLY)

8

CBI0-7

相關PDF資料 |

PDF描述 |

|---|---|

| IDT49FCT818AEB | 8-BIT, DSP-PIPELINE REGISTER, CDFP24 |

| IDT49FCT818P | 8-BIT, DSP-PIPELINE REGISTER, PDIP24 |

| IDT49FCT818L | 8-BIT, DSP-PIPELINE REGISTER, CQCC28 |

| IDT49FCT818LB | 8-BIT, DSP-PIPELINE REGISTER, CQCC28 |

| IDT49FCT818PB | 8-BIT, DSP-PIPELINE REGISTER, PDIP24 |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| IDT49C465PQFB | 制造商:IDT 制造商全稱:Integrated Device Technology 功能描述:32-BIT FLOW-THRU ERROR DETECTION AND CORRECTION UNIT |

| IDT49C466 | 制造商:IDT 制造商全稱:Integrated Device Technology 功能描述:64-BIT FLOW-THRU ERROR DETECTION AND CORRECTION UNIT |

| IDT49C466A | 制造商:IDT 制造商全稱:Integrated Device Technology 功能描述:64-BIT FLOW-THRU ERROR DETECTION AND CORRECTION UNIT |

| IDT49C466APQF | 制造商:IDT 制造商全稱:Integrated Device Technology 功能描述:64-BIT FLOW-THRU ERROR DETECTION AND CORRECTION UNIT |

| IDT49C466GB | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Error Detection & Correction (EDAC) |

發(fā)布緊急采購,3分鐘左右您將得到回復。