- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄296205 > ICS9248YF-153-T (INTEGRATED DEVICE TECHNOLOGY INC) 133.33 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO48 PDF資料下載

參數(shù)資料

| 型號(hào): | ICS9248YF-153-T |

| 廠商: | INTEGRATED DEVICE TECHNOLOGY INC |

| 元件分類: | XO, clock |

| 英文描述: | 133.33 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO48 |

| 封裝: | 0.300 INCH, SSOP-48 |

| 文件頁(yè)數(shù): | 5/14頁(yè) |

| 文件大?。?/td> | 293K |

| 代理商: | ICS9248YF-153-T |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)當(dāng)前第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)

13

ICS9248-153

Third party brands and names are the property of their respective owners.

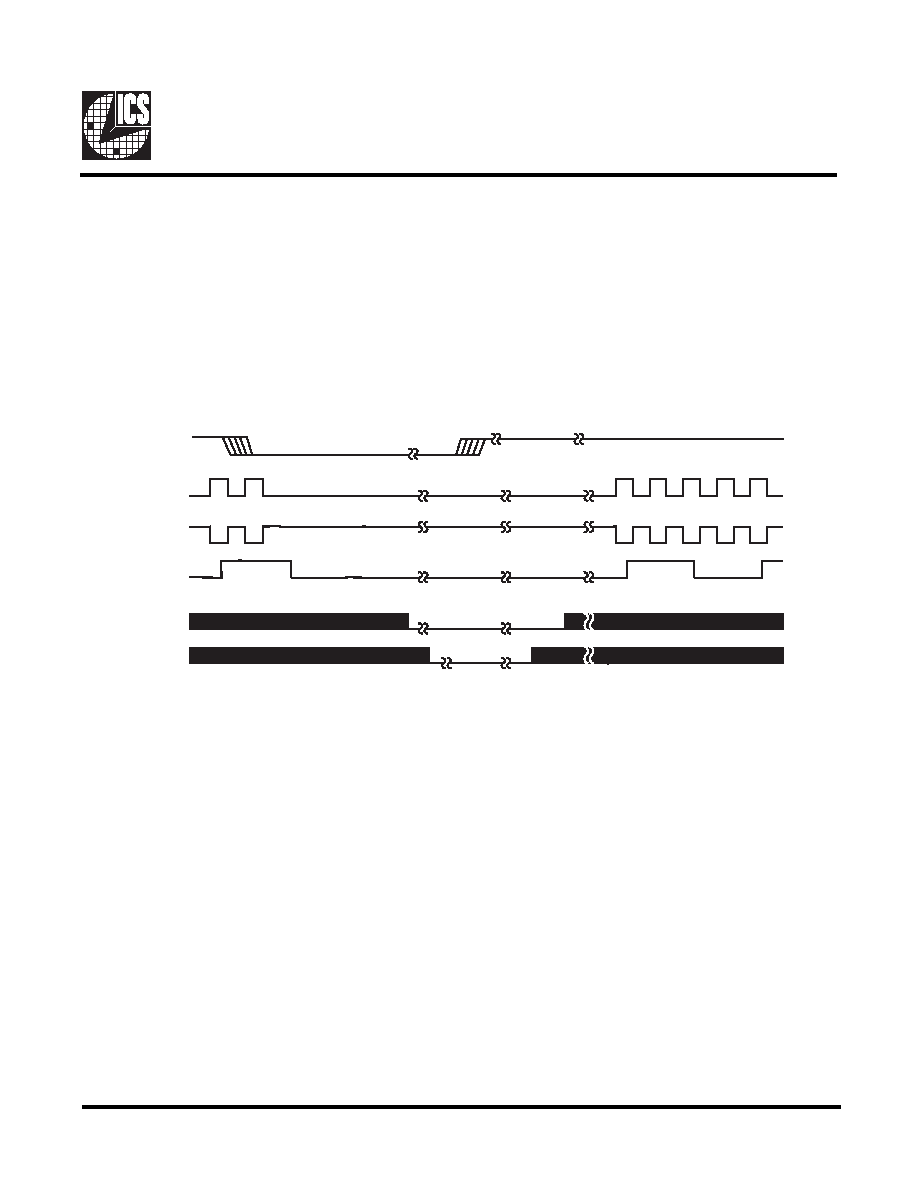

PD# Timing Diagram

The power down selection is used to put the part into a very low power state without turning off the power to the part. PD# is

an asynchronous active low input. This signal needs to be synchronized internal to the device prior to powering down the

clock synthesizer.

Internal clocks are not running after the device is put in power down. When PD# is active low all clocks need to be driven to

a low value and held prior to turning off the VCOs and crystal. The power up latency needs to be less than 3 mS. The power

down latency should be as short as possible but conforming to the sequence requirements shown below. PCI_STOP# and

CPU_STOP# are considered to be don't cares during the power down operations. The REF and 48MHz clocks are expected to

be stopped in the LOW state as soon as possible. Due to the state of the internal logic, stopping and holding the REF clock

outputs in the LOW state may require more than one clock cycle to complete.

Notes:

1. All timing is referenced to the Internal CPUCLK (defined as inside the ICS9248-153 device).

2. As shown, the outputs Stop Low on the next falling edge after PD# goes low.

3. PD# is an asynchronous input and metastable conditions may exist. This signal is synchronized inside this part.

4. The shaded sections on the VCO and the Crystal signals indicate an active clock.

5. Diagrams shown with respect to 133MHz. Similar operation when CPU is 100MHz.

CPUCLKT

CPUCLKC

PCICLK

VCO

Crystal

PD#

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| ICS950218YF-T-LF | 200.4 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO48 |

| ICS950805YF-T | 200 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO56 |

| ICS950805YFLF-T | 200 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO56 |

| ICS950905YFLFT | 200.4 MHz, OTHER CLOCK GENERATOR, PDSO48 |

| ICS951704YFLFT | 166 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO48 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| ICS9248YF-157-T | 制造商:ICS 制造商全稱:ICS 功能描述:Frequency Timing Generator for Pentium II Systems |

| ICS9248YF-163-T | 制造商:ICS 制造商全稱:ICS 功能描述:AMD - K7⑩ System Clock Chip |

| ICS9248YF-168-T | 制造商:ICS 制造商全稱:ICS 功能描述:AMD - K7⑩ Clock Generator for Mobile System |

| ICS9248YF-171-T | 制造商:ICS 制造商全稱:ICS 功能描述:AMD - K7TM System Clock Chip |

| ICS9248YF-189-T | 制造商:ICS 制造商全稱:ICS 功能描述:AMD - K7⑩ Clock Generator for Mobile System |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。