- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄67682 > IBM25PPC405GPR3DB400Z 32-BIT, 400 MHz, RISC PROCESSOR, PBGA456 PDF資料下載

參數(shù)資料

| 型號: | IBM25PPC405GPR3DB400Z |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | 32-BIT, 400 MHz, RISC PROCESSOR, PBGA456 |

| 封裝: | 27 X 27 MM, ENHANCED, PLASTIC, BGA-456 |

| 文件頁數(shù): | 27/58頁 |

| 文件大?。?/td> | 1264K |

| 代理商: | IBM25PPC405GPR3DB400Z |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁當前第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁

Preliminary

PowerPC 405GPr Embedded Processor Data Sheet

3/14/03

Page 33 of 58

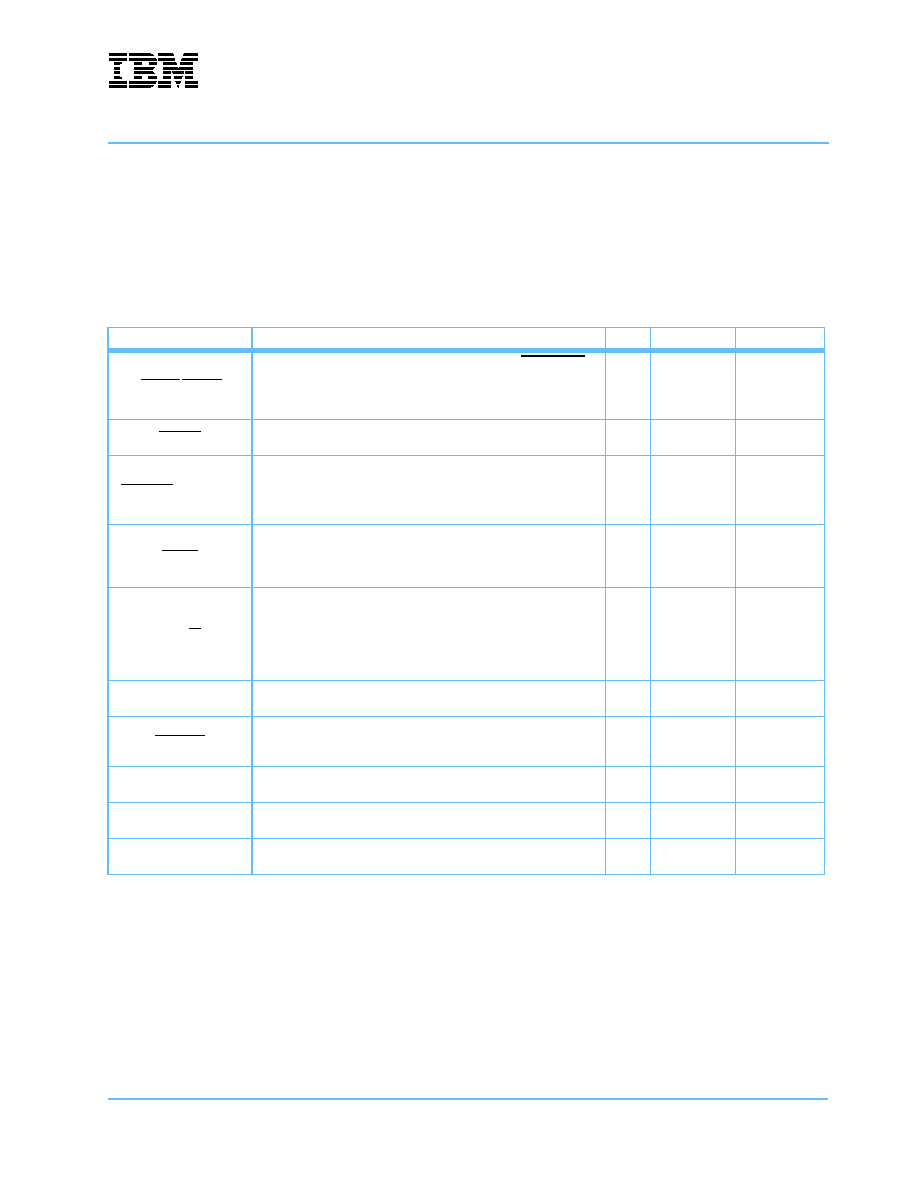

[PerWE]PCIINT

Peripheral write enable. Low when any of the four PerWBE0:3

write byte enables are low.

or

PCI interrupt. Open-drain output (two states; 0 or open circuit)

O

5V tolerant

3.3V PCI

PerCS0

Peripheral chip select bank 0.

O

5V tolerant

3.3V LVTTL

7

PerCS1:7[GPIO10:16]

Seven additional peripheral chip selects

or

General Purpose I/O. To access this function, software must

toggle a DCR bit.

O[I/O]

5V tolerant

3.3V LVTTL

1, 7

PerOE

Used by either the peripheral controller or the DMA controller

depending upon the type of transfer involved. When the

PPC405GPr is the bus master, it enables the selected device to

drive the bus.

O

5V tolerant

3.3V LVTTL

7

PerR/W

Used by the PPC405GPr when not in external master mode, as

output by either the peripheral controller or DMA controller

depending upon the type of transfer involved. High indicates a

read from memory, low indicates a write to memory.

Otherwise it used by the external master as an input to indicate

the direction of data transfer.

I/O

5V tolerant

3.3V LVTTL

1

PerReady

Used by a peripheral slave to indicate it is ready to transfer data.

I

5V tolerant

3.3V LVTTL

1

PerBLast

Used by the PPC405GPr when not in external master mode,

otherwise used by external master. Indicates the last transfer of a

memory access.

I/O

5V tolerant

3.3V LVTTL

1, 7

DMAReq0:3

DMAReq0:3 are used by slave peripherals to indicate they are

prepared to transfer data.

I

5V tolerant

3.3V LVTTL

1

DMAAck0:3

DMAAck0:3 are used by the PPC405GPr to cause the DMA

peripheral to transfer data.

O

5V tolerant

3.3V LVTTL

6

EOT0:3/TC0:3

End Of Transfer/Terminal Count.

I/O

5V tolerant

3.3V LVTTL

1

Signal Functional Description (Part 4 of 8)

Multiplexed signals are shown in brackets following the first signal name assigned to each multiplexed ball.

Notes:

1. Receiver input has hysteresis.

2. Must pull up. See “Pull-Up and Pull-Down Resistors” on page 29 for recommended termination values.

3. Must pull down. See “Pull-Up and Pull-Down Resistors” on page 29 for recommended termination values.

4. If not used, must pull up.

5. If not used, must pull down.

6. Strapping input during reset; pull up or pull down as required.

7. Pull-up may be required. See “External Bus Control Signals” on page 29.

Signal Name

Description

I/OType

Notes

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| IBM25PPC405GPR3BB400Z | 32-BIT, 400 MHz, RISC PROCESSOR, PBGA456 |

| IBM25PPC405GPR3DB266 | 32-BIT, 266 MHz, RISC PROCESSOR, PBGA456 |

| IBM25PPC603E-BX-133X | 32-BIT, 133 MHz, RISC PROCESSOR, CBGA255 |

| IBM25PPC603EV-FX-233X | 32-BIT, 233 MHz, RISC PROCESSOR, CQFP240 |

| IBM25PPC603EV-FX-225X | 32-BIT, 225 MHz, RISC PROCESSOR, CQFP240 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| IBM25PPC405-GPR-3JB266Z | 制造商:IBM 功能描述: |

| IBM25PPC405GPR-3KB266C | 制造商:IBM 功能描述: |

| IBM25PPC440GX3CB667C | 制造商:IBM 功能描述: |

| IBM25PPC603E-BX-080-X | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:32-Bit Microprocessor |

| IBM25PPC603E-BX-100-X | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:32-Bit Microprocessor |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。