- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄383075 > HSP50214A (Intersil Corporation) Programmable Downconverter PDF資料下載

參數(shù)資料

| 型號(hào): | HSP50214A |

| 廠商: | Intersil Corporation |

| 英文描述: | Programmable Downconverter |

| 中文描述: | 可編程變頻器 |

| 文件頁(yè)數(shù): | 15/60頁(yè) |

| 文件大小: | 467K |

| 代理商: | HSP50214A |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)當(dāng)前第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)

15

CIC Gain Calculations

The gain through the CIC filter increases with increased dec-

imation. The programmable barrel shifter that precedes the

first integrator in the CIC is used to offset this variation. Gain

variations due to decimation should be offset using the 4-bit

CIC Shift Gain word. This allows the input signal level to be

adjusted in 6dB steps to control the CIC output level.

The gain at each stage of the CIC is:

R

N

,

=

where R is the decimation factor and N is the number of stages.

The input to the CIC from the mixer is 15 bits, and the bit widths

of the accumulators for the five stages in the HSP50214A are

40, 36, 32, 32, and 32, as shown in Figure 16. This limits the

maximum decimation in the CIC to 32 for a full scale input.

If R is 32, the gain through all five integrator stages is 32

5

= 2

25

.

(The gain through the last four CIC stages is 2

20

, through the

last 3 it is 2

15

, etc.). The sum of the input bits and the growth

bits cannot exceed the accumulator size. This means that for a

decimation of 32 and 15 input bits, the first accumulator must

be 15 + 25 = 40 bits.

Thus, the value of the CIC Shift Gain word can be calcu-

lated:

NOTE: The number of input bits is IIN. (If the number of bits into

the CIC filter is used, the value 40 replaces 39).

For 14 bits, Equation 7 becomes:

For 12 bits, Equation 7 becomes:

For 10 bits, Equation 7 becomes:

For 8 bits, Equation 7 becomes:

Figure 15 is a plot of Equations 8A through 8D. The 4-bit CIC

Shift Gain word has a range from 0 to 15. The 6-bit CIC Dec-

imation Factor Counter Preload field, (R-1), has a range from

0 to 63, limited by the input resolution as cited above.

Using the Input Gain Adjust Control Signals

The input gain offset control GAINADJ(2:0)) is provided to offset

the signal gain through the part, i.e., to keep the CIC filter output

level constant as the analog front end attenuation is changed.

Thegainadjustoffsetis6dBpercode,sothegainadjustrangeis

0 to 42dB. For example, if 12dB of attenuation is switched in at

the receiver RF front end, a code of 2 would increase the gain at

the input to the CIC filter up 12dB so that the CIC filter output

would not drop by 12dB. This fixed gain adjust eliminates the

need for the software to continually normalize.

One must exercise care when using this function as it can

cause overflow in the CIC filter. Each gain adjust in the

shifter from the gain adjust control signals is the equivalent

of an extra bit of input. The maximum decimation in the CIC

is reduced accordingly. With a decimation of 32, all 40 bits of

the CIC are needed, so no input offset gain is allowed. As

the decimation is reduced, the allowable offset gain

increases. Table 3 shows the decimation range versus

desired offset gain range. Table 3 assumes that the CIC Shift

Gain has been programmed per Equation 7 or 8A.

The CIC filter decimation counter can be loaded synchronous

with other PDC chips, using the SYNCIN1 signal and the CIC

External Sync Enable bit. The CIC external Sync Enable is set

via Control Word 0, Bit 19.

Halfband Decimating Filters

The Programmable Down Converter has five halfband filter

stages, as shown in Figure 17. Each stage decimates by 2

and filters out half of the available bandwidth. The first half-

band, or HB1, has 7 taps. The remaining halfbands; HB2,

HB3, HB4, and HB5; have 11, 15, 19, and 23 taps respec-

tively. The coefficients for these halfbands are given in Table

4. Figure 18 shows the frequency response of each of the

halfband filters with respect to normalized frequency, F

N

.

Frequency normalization is with respect to the input sam-

pling frequency of each filter section. Each stage is activated

by their respective bit location (15-20) in Control Word 7. Any

combination of halfband filters may be used, or all may be

bypassed.

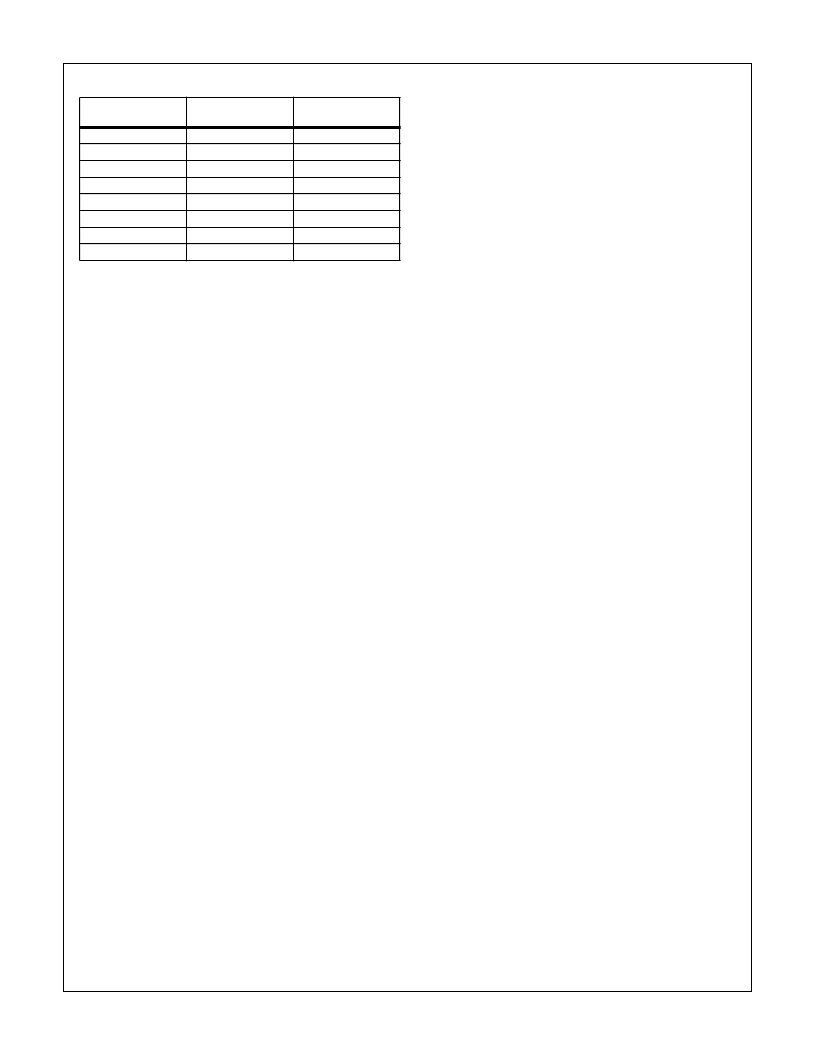

TABLE 3. GAIN ADJUST CONTROL AND CIC DECIMATION

GAIN VALUE

(dB)

GAIN ADJ(2:0)

0

000

6

001

12

010

18

011

24

100

30

101

36

110

42

111

MAX. CIC

DECIMATION

32

27

24

21

18

16

12

10

k

(EQ. 6)

(EQ. 7)

SG = FLOOR 39 -

IIN

(

)

- log

2

(R)

5

for 4<R<32

for R = 4

= 15

SG

FLOOR 25

= 15

log

2

R

( )

5

]

for 4

R

32

<

<

4

–

=

15

for R

=

(EQ. 8A)

SG

FLOOR 27

15

log

2

R

( )

5

]

for 5 < R < 40

for 4

–

=

=

(EQ. 8B)

R

5

≤

≤

SG

FLOOR 29

15

log

2

R

( )

5

]

for 6 < R < 52

for 4

–

=

=

(EQ. 8C)

R

6

≤

≤

SG

FLOOR 31

log

2

R

( )

5

]

for 9 < R < 64

for 4

–

=

(EQ. 8D)

15

=

R

9

≤

≤

HSP50214A

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| HSP50214AVC | Programmable Downconverter |

| HSP50214AVI | Programmable Downconverter |

| HSP50214B | Programmable Downconverter |

| HSP50214BVC | Programmable Downconverter |

| HSP50214BVI | Programmable Downconverter |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| HSP50214AVC | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| HSP50214AVI | 制造商:INTERSIL 制造商全稱(chēng):Intersil Corporation 功能描述:Programmable Downconverter |

| HSP50214B | 制造商:INTERSIL 制造商全稱(chēng):Intersil Corporation 功能描述:Programmable Downconverter |

| HSP50214B_07 | 制造商:INTERSIL 制造商全稱(chēng):Intersil Corporation 功能描述:Programmable Downconverter |

| HSP50214BVC | 功能描述:上下轉(zhuǎn)換器 120L MQFP COMTEMP 14-BIT PROGRAMMABLE DOWNCONVERTER 65MSPS RoHS:否 制造商:Texas Instruments 產(chǎn)品:Down Converters 射頻:52 MHz to 78 MHz 中頻:300 MHz LO頻率: 功率增益: P1dB: 工作電源電壓:1.8 V, 3.3 V 工作電源電流:120 mA 最大功率耗散:1 W 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:PQFP-128 |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。