- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄370451 > HCPL-316J 2.0 Amp Gate Drive Optocoupler with Integrated (V CE ) Desaturation Detection and Fault Status Feedback(帶集成不飽和檢測(cè)和誤差反饋的2.0 Amp門驅(qū)動(dòng)耦合器) PDF資料下載

參數(shù)資料

| 型號(hào): | HCPL-316J |

| 英文描述: | 2.0 Amp Gate Drive Optocoupler with Integrated (V CE ) Desaturation Detection and Fault Status Feedback(帶集成不飽和檢測(cè)和誤差反饋的2.0 Amp門驅(qū)動(dòng)耦合器) |

| 中文描述: | 2.0安培門極驅(qū)動(dòng)光電耦合器與集成(五長官)飽和檢測(cè)與故障狀態(tài)反饋(帶集成不飽和檢測(cè)和誤差反饋的2.0安培門驅(qū)動(dòng)耦合器) |

| 文件頁數(shù): | 26/32頁 |

| 文件大?。?/td> | 503K |

| 代理商: | HCPL-316J |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁當(dāng)前第26頁第27頁第28頁第29頁第30頁第31頁第32頁

26

gate control signal is a

continuous PWM signal, the fault

latch will always be reset by the

next time the input signal goes

high. This configuration protects

the IGBT on a cycle-by-cycle

basis and automatically resets

before the next ‘on’ cycle. The

fault outputs can be wire ‘OR’ed

together to alert the

microcontroller, but this signal

would not be used for control

purposes in this (Auto-Reset)

configuration. When the

HCPL- 316J is configured for

Auto-Reset, the guaranteed

minimum FAULT signal pulse

width is 3

μ

s.

HCPL-316J

Resetting Following a Fault

Condition

To resume normal switching

operation following a fault

condition (FAULT output low),

the RESET pin must first be

asserted low in order to release

the internal fault latch and reset

the FAULT output (high). Prior to

asserting the RESET pin low, the

input (V

IN

) switching signals must

be configured for an output (V

OL

)

low state. This can be handled

directly by the microcontroller or

by hardwiring to synchronize the

RESET signal with the

appropriate input signal. Figure

73a shows how to connect the

RESET to the V

IN+

signal for safe

automatic reset in the non-

inverting input configuration.

Figure 73b shows how to

configure the V

IN+

/RESET signals

so that a RESET signal from the

microcontroller causes the input

to be in the “output-off” state.

Similarly, Figures 73c and 73d

show automatic RESET and

microcontroller RESET safe

configurations for the inverting

input configuration.

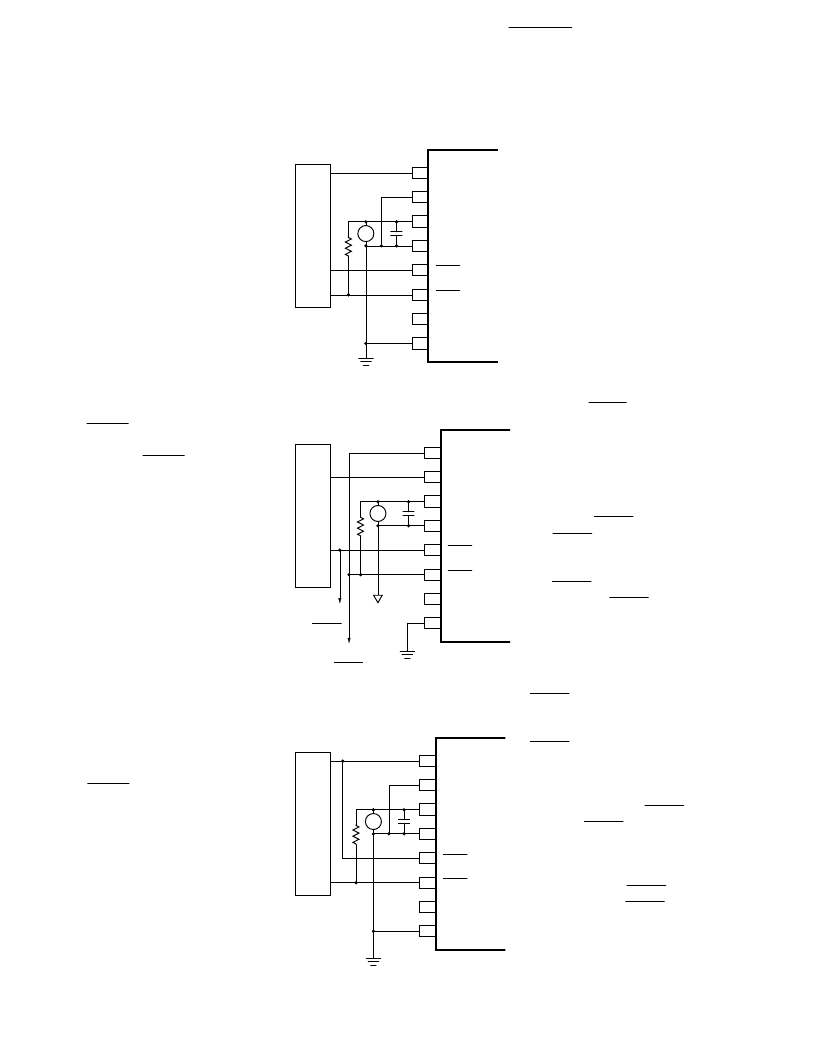

Local Shutdown, Local Reset

As shown in Figure 70, the fault

output of each HCPL-316J gate

driver is polled separately, and

the individual reset lines are

asserted low independently to

reset the motor controller after a

fault condition.

Global-Shutdown, Global

Reset

As shown in Figure 71, when

configured for inverting

operation, the HCPL-316J can be

configured to shutdown

automatically in the event of a

fault condition by tying the

FAULT output to V

IN+

. For high

reliability drives, the open

collector FAULT outputs of each

HCPL-316J can be wire ‘OR’ed

together on a common fault bus,

forming a single fault bus for

interfacing directly to the micro-

controller. When any of the six

gate drivers detects a fault, the

fault output signal will disable all

six HCPL-316J gate drivers

simultaneously and thereby

provide protection against further

catastrophic failures.

Auto-Reset

As shown in Figure 72, when the

inverting V

IN-

input is connected

to ground (non-inverting

configuration), the HCPL-316J

can be configured to reset

automatically by connecting

RESET to V

IN+

. In this case, the

gate control signal is applied to

the non-inverting input as well as

the reset input to reset the fault

latch every switching cycle.

During normal operation of the

IGBT, asserting the reset input

low has no effect. Following a

fault condition, the gate driver

remains in the latched fault state

until the gate control signal

changes to the ‘gate low’ state

and resets the fault latch. If the

Figure 71. Global-Shutdown, Global

Reset Configuration.

Figure 72. Auto-Reset Configuration.

Figure 70. Local Shutdown, Local

Reset Configuration.

1

2

3

4

5

6

7

8

V

IN+

V

IN-

V

CC1

GND1

RESET

FAULT

V

LED1+

V

LED1-

HCPL-316J

+

–

μC

1

2

3

4

5

6

7

8

V

IN+

V

IN-

V

CC1

GND1

RESET

FAULT

V

LED1+

V

LED1-

+

–

μC

CONNECT

TO OTHER

FAULTS

CONNECT

TO OTHER

RESETS

1

2

3

4

5

6

7

8

V

IN+

V

IN-

V

CC1

GND1

RESET

FAULT

V

LED1+

V

LED1-

HCPL-316J

+

–

μC

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| HCPL-3700 | AC/DC to Logic Interface Optocouplers(AC/DC邏輯接口光耦合器) |

| HCPL-4100300 | Optically Coupled 20 mA Current Loop Transmitter |

| HCPL-4100500 | Optically Coupled 20 mA Current Loop Transmitter |

| HCPL4100 | Optically Coupled 20 mA Current Loop Transmitter |

| HCPL-4100 | Optically Coupled 20 mA Optically Coupled 20 mA |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| HCPL-316J#500 | 功能描述:邏輯輸出光電耦合器 2.0A IGBT Gate Drive RoHS:否 制造商:Fairchild Semiconductor 絕緣電壓:4243 Vrms 輸出類型:Push-Pull 最大傳播延遲時(shí)間:500 ns 最大正向二極管電壓: 最大反向二極管電壓: 最大正向二極管電流: 最大連續(xù)輸出電流:2.5 A 最大功率耗散:100 mW 最大工作溫度:+ 100 C 最小工作溫度:- 40 C 封裝 / 箱體:SO-16 封裝:Tube |

| HCPL-316J-000E | 功能描述:邏輯輸出光電耦合器 2.0A IGBT Gate Drive RoHS:否 制造商:Fairchild Semiconductor 絕緣電壓:4243 Vrms 輸出類型:Push-Pull 最大傳播延遲時(shí)間:500 ns 最大正向二極管電壓: 最大反向二極管電壓: 最大正向二極管電流: 最大連續(xù)輸出電流:2.5 A 最大功率耗散:100 mW 最大工作溫度:+ 100 C 最小工作溫度:- 40 C 封裝 / 箱體:SO-16 封裝:Tube |

| HCPL-316J-000E | 制造商:Avago Technologies 功能描述:GATE DRIVE OPTOCOUPLERLF - LEAD FREE VE |

| HCPL-316J-500E | 功能描述:邏輯輸出光電耦合器 2.0A IGBT Gate Drive RoHS:否 制造商:Fairchild Semiconductor 絕緣電壓:4243 Vrms 輸出類型:Push-Pull 最大傳播延遲時(shí)間:500 ns 最大正向二極管電壓: 最大反向二極管電壓: 最大正向二極管電流: 最大連續(xù)輸出電流:2.5 A 最大功率耗散:100 mW 最大工作溫度:+ 100 C 最小工作溫度:- 40 C 封裝 / 箱體:SO-16 封裝:Tube |

| HCPL-3180 | 功能描述:高速光耦合器 2.0A IGBT Gate Drive RoHS:否 制造商:Avago Technologies 電流傳遞比: 最大波特率: 最大正向二極管電壓:1.75 V 最大反向二極管電壓:5 V 最大功率耗散:40 mW 最大工作溫度:+125 C 最小工作溫度:- 40 C 封裝 / 箱體:SOIC-5 封裝:Tube |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。