- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄97867 > DS2196LN (DALLAS SEMICONDUCTOR) DATACOM, FRAMER, PQFP100 PDF資料下載

參數(shù)資料

| 型號(hào): | DS2196LN |

| 廠商: | DALLAS SEMICONDUCTOR |

| 元件分類: | Digital Transmission Controller |

| 英文描述: | DATACOM, FRAMER, PQFP100 |

| 封裝: | LQFP-100 |

| 文件頁(yè)數(shù): | 13/160頁(yè) |

| 文件大小: | 559K |

| 代理商: | DS2196LN |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)當(dāng)前第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)第75頁(yè)第76頁(yè)第77頁(yè)第78頁(yè)第79頁(yè)第80頁(yè)第81頁(yè)第82頁(yè)第83頁(yè)第84頁(yè)第85頁(yè)第86頁(yè)第87頁(yè)第88頁(yè)第89頁(yè)第90頁(yè)第91頁(yè)第92頁(yè)第93頁(yè)第94頁(yè)第95頁(yè)第96頁(yè)第97頁(yè)第98頁(yè)第99頁(yè)第100頁(yè)第101頁(yè)第102頁(yè)第103頁(yè)第104頁(yè)第105頁(yè)第106頁(yè)第107頁(yè)第108頁(yè)第109頁(yè)第110頁(yè)第111頁(yè)第112頁(yè)第113頁(yè)第114頁(yè)第115頁(yè)第116頁(yè)第117頁(yè)第118頁(yè)第119頁(yè)第120頁(yè)第121頁(yè)第122頁(yè)第123頁(yè)第124頁(yè)第125頁(yè)第126頁(yè)第127頁(yè)第128頁(yè)第129頁(yè)第130頁(yè)第131頁(yè)第132頁(yè)第133頁(yè)第134頁(yè)第135頁(yè)第136頁(yè)第137頁(yè)第138頁(yè)第139頁(yè)第140頁(yè)第141頁(yè)第142頁(yè)第143頁(yè)第144頁(yè)第145頁(yè)第146頁(yè)第147頁(yè)第148頁(yè)第149頁(yè)第150頁(yè)第151頁(yè)第152頁(yè)第153頁(yè)第154頁(yè)第155頁(yè)第156頁(yè)第157頁(yè)第158頁(yè)第159頁(yè)第160頁(yè)

DS2196

11 of 160

Framer Loopback A

Payload Loopback A

AIS & AIS-CI Generation

B8ZS Encode

CRC Generation

Yellow Alarm Generation

Signaling Insertion

Clear Channel

F-Bit Insertion

P

ara

ll

el

C

o

n

tro

l

P

o

rt

(r

ou

te

d

t

o

al

lb

lock

s)

R

ece

ive

S

ide

Fr

am

er

A

Tr

an

sm

it

S

id

e

Fo

rm

at

te

rA

BPV Counter

Alarm Detection

Loop Code Generation

fs

y

n

c

da

ta

clo

ck

ms

y

n

c

da

ta

cl

ock

D0 to D7 /

AD0 to AD7

BTS

INT*

TSYNCA

TCLKA

TCHCLKA/

TLCLKA

TSERA

TCHBLKA/

TLINKA

WR*(R/W*)

RD*(DS*)

RCHCLKA/

RLCLKA

CS*

RCHBLKA/

RLINKA

RMSYNCA

RSERA

RFSYNCA

FDL

E

x

tr

a

c

ti

o

n

FD

L

I

n

se

rt

io

n

B8ZS Decoder

Synchronizer

Loop Code Detector

CRC/Frame Error Count

Signaling Extraction

Channel Marking

RLOSA / LOTCA

ALE(AS) / A7

A0 to A6

MUX

8

RCL

Line Drivers

CSU Filters

Wave Shaping

Local Loopback

TR

IN

G

TT

IP

Jitter Attenuation

(can be placed in either transmit or receive path)

Filter

Peak Detect

Clock / Data

Recovery

RR

IN

G

RT

IP

Remote Loopback

VCO

/

PLL

MC

L

K

1.

54

4

M

H

z

LIU AIS Generation

RCLKA

7

RPOSLO

RNEGLO

RNEGIA

RPOSIA

TPOSLI

TNEGLI

TNEGOA/

TFSYNCA

TPOSOA/

TNRZA

RCLKLO

RCLKIA

Per-Channel Loopback

TCLKLI

TCLKOA

64

-B

yt

e

B

u

ff

er

BO

M

D

e

te

c

ti

o

n

64

-B

yt

e

B

u

ff

er

B

O

M

G

en

era

tio

n

m

u

x

(

con

tr

ol

le

d

vi

a

C

R

4

A

.2)

m

u

x

(c

o

n

tro

lle

d

vi

a

C

R

4

A

.2)

ms

y

n

c

fs

y

n

c

Framer Loopback B

AIS & AIS-CI Generation

B8ZS Encode

CRC Generation

Yellow Alarm Generation

Signaling Insertion

Clear Channel

F-Bit Insertion

Tr

an

sm

it

S

id

e

Fo

rm

at

te

rB

BPV Counter

Alarm Detection

Loop Code Generation

fs

y

n

c

da

ta

cl

ock

ms

y

n

c

da

ta

cl

o

c

k

FD

L

E

x

tr

a

ct

io

n

FDL

I

n

se

rt

io

n

B8ZS Decoder

Synchronizer

Loop Code Detector

CRC/Frame Error Count

Signaling Extraction

Channel Marking

Per-Channel Loopback

64

-B

yt

e

B

u

ff

er

B

O

M

D

e

te

ct

io

n

64

-B

yt

e

B

u

ff

er

B

O

M

G

ener

at

ion

ms

y

n

c

fs

y

n

c

TS

YNC

Co

n

tr

o

l

T

S

YNC

Co

n

tr

o

l

Cl

o

ck

Ge

n

Cl

o

ck

Ge

n

Cl

o

c

k

Ge

n

TSYNCB

TCLKB

TSERB

TCHCLKB

TLCLKB

TCHBLKB/

TLINKB

RLOSB / LOTCB

RCHCLKB/

RLCLKB

RCHBLKB/

RLINKB

RCLKB

RMSYNCB

RSERB

RFSYNCB

LI

U

AI

S

PRO-

TEC

T

WO

R

K

-

IN

G

WPS

WN

R

Z

WC

L

K

PNRZ

PCLK

TN

E

G

o

rTF

S

Y

N

C

TCL

K

TP

O

S

o

rT

N

R

Z

L

FSYNC

LCL

K

LN

R

Z

m

u

x

(

co

n

tr

ol

le

d

v

ia

C

R4

B.

2

)

RPOS

IB

RNEG

IB

RC

L

K

IB

T

P

OS

OB

/

TN

R

Z

B

TC

L

K

O

B

TN

E

G

O

B

/

T

FSY

NC

B

R

ece

ive

S

ide

Fr

am

er

B

Cl

o

c

k

Ge

n

To

BE

R

T

Mu

x

JT

A

G

JTCLK

JTMS

JTDO

JTDI

JTRST*

To

BE

R

T

Mu

x

Insert Data From BERT

POWER

DVSS

(3

)

RVSS

(2

)

T

VDD

TV

S

RVDD

DVDD

(3

)

BE

R

T

M

u

x

RXA

RXB

TX

A

4

5

To

/

Fr

om

BE

R

T

M

u

x

RBPVA

RBPVB

Da

ta

So

u

rc

e

M

UX

C

o

n

tr

o

l

(c

o

n

tro

lle

d

v

ia

CC

R1

A

.2

/3

/4

)

Back End Loopback

RSER

RMSYNC

RCLK

SYSCLK

SSER

SFSYNC

D

S

21

75

(o

p

tio

n

al)

fr

om

R

e

cei

ve

F

ram

er

B

(o

n

ly

in

F

T

1

ap

p

lic

at

io

n

)

ms

y

n

c

1.

54

4M

H

z

RC

L

K

B

RM

SYN

C

B

Us

e

r

Ou

tp

u

t

Por

t(

4

pi

n

s)

UOP0

UOP1

UOP2

UOP3

FL

B

2

FLB B Mux

F

ro

m

BERT

M

u

x

LO

T

C

M

u

x

Fr

om

MC

L

K

4

BE

R

T

clock

data

clock

data

Corrupt F-Bit / Payload

sync

Payload Loopback B

mu

x

(c

o

n

tr

o

ll

ed

v

ia

C

CR4

B.

2

)

LOTC

M

u

x

Fr

om

MC

L

K

LN

R

Z

A

IS

G

ener

at

ion

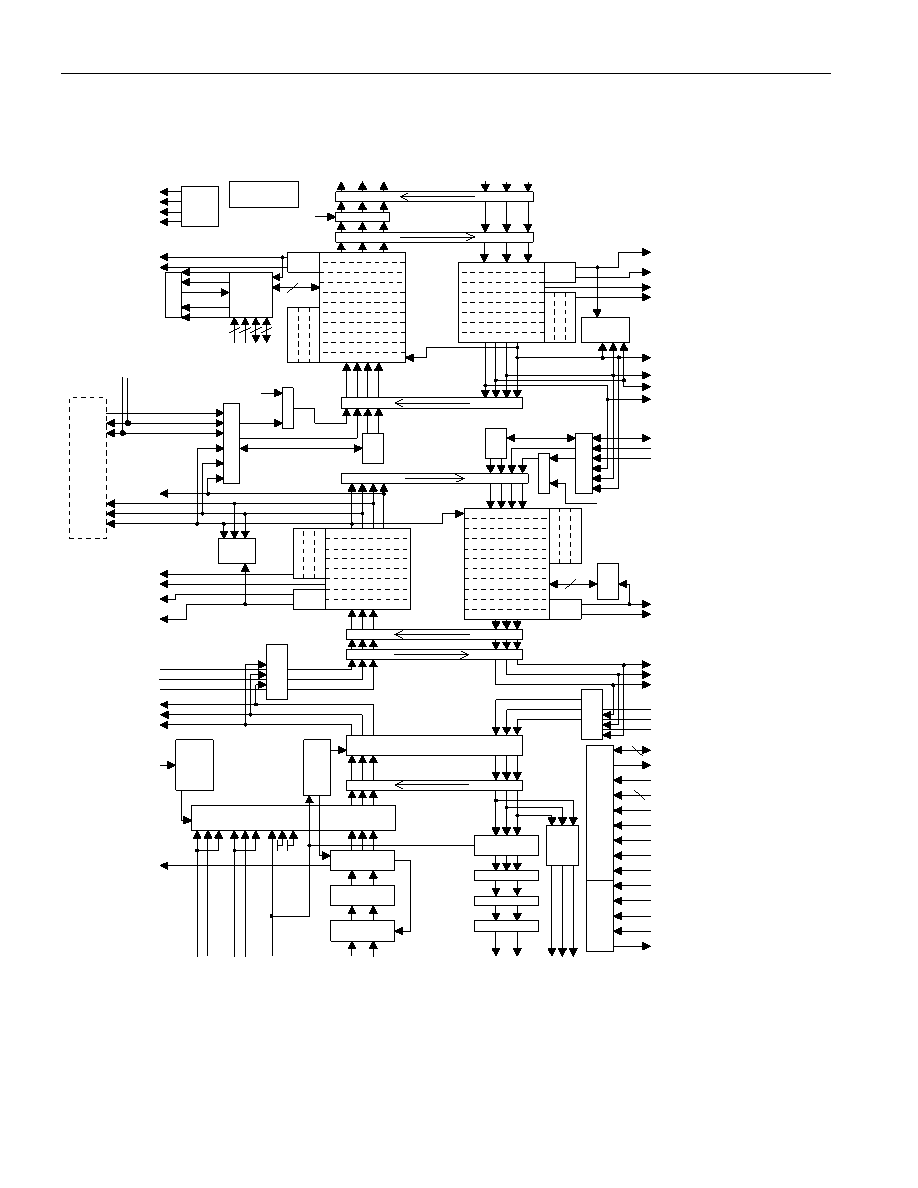

Figure 1-1: T1 DUAL FRAMER LIU

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| DS21FF44 | DATACOM, FRAMER, PBGA300 |

| DS21FF44N | DATACOM, FRAMER, PBGA300 |

| DS21FT40N | DATACOM, FRAMER, PBGA300 |

| DS21FT40 | DATACOM, FRAMER, PBGA300 |

| DS21FT42 | DATACOM, FRAMER, PBGA300 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| DS2196LN+ | 功能描述:網(wǎng)絡(luò)控制器與處理器 IC T1 Dual Framer LIU RoHS:否 制造商:Micrel 產(chǎn)品:Controller Area Network (CAN) 收發(fā)器數(shù)量: 數(shù)據(jù)速率: 電源電流(最大值):595 mA 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:PBGA-400 封裝:Tray |

| DS219T | 功能描述:烙鐵 DESOLDERING HEAD RoHS:否 制造商:Weller 產(chǎn)品:Soldering Stations 類型:Digital, Iron, Stand, Cleaner 瓦特:50 W 最大溫度:+ 850 F 電纜類型:US Cord Included |

| DS21E352 | 功能描述:網(wǎng)絡(luò)控制器與處理器 IC RoHS:否 制造商:Micrel 產(chǎn)品:Controller Area Network (CAN) 收發(fā)器數(shù)量: 數(shù)據(jù)速率: 電源電流(最大值):595 mA 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:PBGA-400 封裝:Tray |

| DS21E352N | 功能描述:網(wǎng)絡(luò)控制器與處理器 IC RoHS:否 制造商:Micrel 產(chǎn)品:Controller Area Network (CAN) 收發(fā)器數(shù)量: 數(shù)據(jù)速率: 電源電流(最大值):595 mA 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:PBGA-400 封裝:Tray |

| DS21E354 | 功能描述:網(wǎng)絡(luò)控制器與處理器 IC RoHS:否 制造商:Micrel 產(chǎn)品:Controller Area Network (CAN) 收發(fā)器數(shù)量: 數(shù)據(jù)速率: 電源電流(最大值):595 mA 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:PBGA-400 封裝:Tray |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。