- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄376802 > DM9102DE (Electronic Theatre Controls, Inc.) SINGLE CHIP FAST ETHEMET NIC CONTROLLER PDF資料下載

參數(shù)資料

| 型號: | DM9102DE |

| 廠商: | Electronic Theatre Controls, Inc. |

| 英文描述: | SINGLE CHIP FAST ETHEMET NIC CONTROLLER |

| 中文描述: | 單晶片快速以太網(wǎng)NIC控制器 |

| 文件頁數(shù): | 7/70頁 |

| 文件大小: | 2245K |

| 代理商: | DM9102DE |

第1頁第2頁第3頁第4頁第5頁第6頁當(dāng)前第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁

Preliminary datasheet

Version: DM9102D-DS-P02

Jan. 14, 2005

7

master device to stop the current transaction.

Parity Error

The DM9102D as a master or slave will assert this signal low

to indicate a parity error on any incoming data.

System Error

This signal is asserted low when address parity is detected

with enabled PCICS bit31 (detected parity error.) The system

error asserts two clock cycles after the falling address if an

address parity error is detected.

Parity

This signal indicates even parity across AD0~AD31 and

C/BE0#~C/BE3# including the PAR pin. This signal is an

output for the master and an input for the slave device. It is

stable and valid one clock after the address phase.

Bus Command/Byte Enable

During the address phase, these signals define the bus

command or the type of bus transaction that will take place.

During the data phase these pins indicate which byte lanes

contain valid data. C/BE0# applies to bit7-0 and C/BE3#

applies to bit31-24.

Address & Data or Boot ROM Address

These are multiplexed address and data bus signals. As a

bus master, the DM9102D will drive address during the first

bus phase. During subsequent phases, the DM9102D will

either read or write data expecting the target to increment its

address pointer. As a target, the DM9102D will decode each

address on the bus and respond if it is the target being

addressed.

AD17~AD0 can also be used as boot ROM address

MA17~MA0 when the boot ROM is accessed.

30

PERR#

I/O

31

SERR#

I/O

33

PAR

I/O

2,20,34,48

C/BE3#

C/BE2#

C/BE1#

C/BE0#

I/O

121,122,123,124,126,127,

128,1,6,7,10,11,13,14,16,

17,38,39,40,41,43,44,47,

49,50,51,54,55,56,57,59,

60

AD31~AD0/

MA17~MA0

I/O

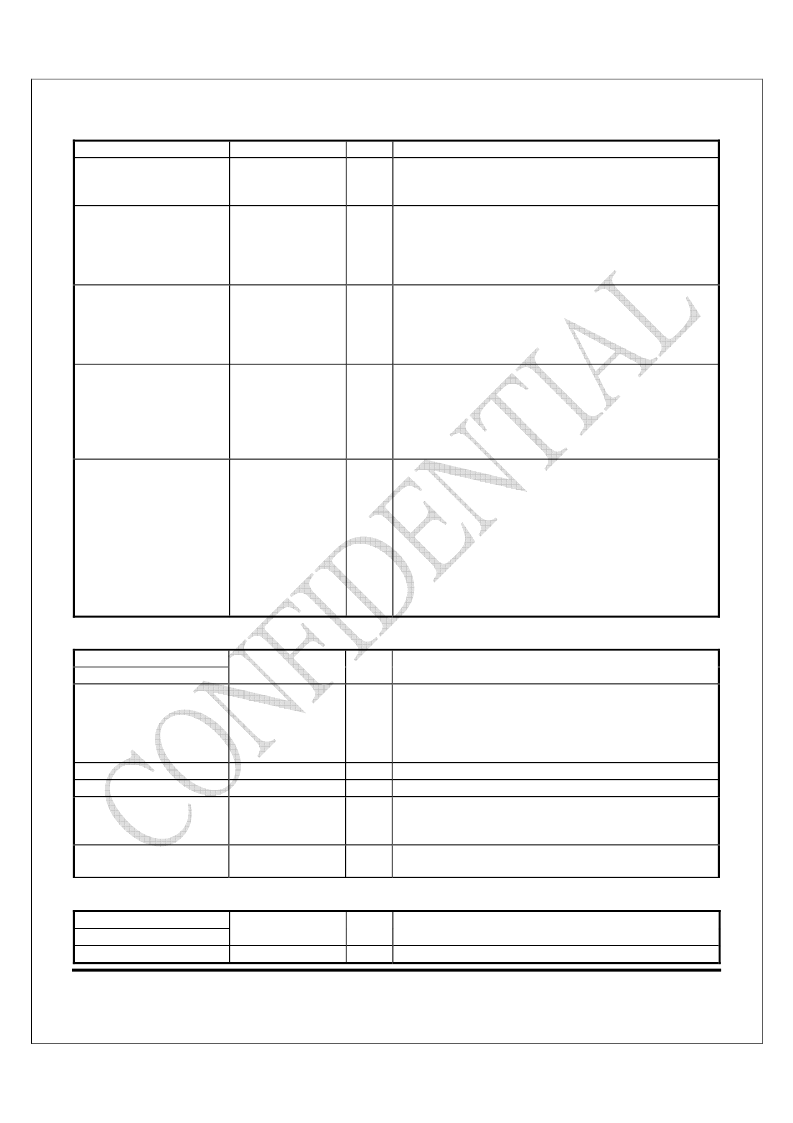

5.2 Boot ROM and EEPROM Interfaces

Pin No.

128LQFP

62

Pin Name

I/O

Description

MD0/EEDI

I

Boot ROM Data Input/EEPROM Data In

This is a multiplexed pin used by EEDI and MD0.

When boot ROM is selected, it acts as boot ROM data input,

otherwise the DM9102D will read the contents of EEPROM

serially through this pin.

Boot ROM Data Input Bus

Boot ROM (active low )or EEPROM Chip Selection.

EEPROM Data Out

This pin is used serially to write op-codes, addresses and

data into the EEPROM.

EEPROM Serial Clock

This pin is used as the clock for the EEPROM data transfer.

63,64,65,66,67,68,69

72

78

MD1~MD7

BPCS#/EECS

EEDO

I

O

O

79

EECK

O

5.3 LED Pins

Pin No.

128LQFP

87

Pin Name

I/O

Description

LINK&ACT#

O/D LED Output Pin, Active Low

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| DM9102 | Single Chip Fast Ethernet NIC controller |

| DM9102A | Single Chip Fast Ethernet NIC controller |

| DM9102AF | Single Chip Fast Ethernet NIC controller |

| DM9102AT | Single Chip Fast Ethernet NIC controller |

| DM9108APPLICATIONENGINEERINGNOTESONE | DM9108 Application Engineering notes one |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| DM9102DEP | 制造商:DAVICOM 功能描述:IC ENET CNTRL 10/100M PHY 1 制造商:DAVICOM 功能描述:IC ENET CNTRL 10/100M PHY 128LQFP 制造商:DAVICOM 功能描述:IC, ENET CNTRL, 10/100M PHY, 128LQFP 制造商:DAVICOM 功能描述:IC, ENET CNTRL, 10/100M PHY, 128LQFP; Data Rate:100Mbps; Ethernet Type:IEEE 802.3u; Supply Voltage Min:2.375V; Supply Voltage Max:2.625V; Digital IC Case Style:LQFP; No. of Pins:128; Interface Type:PCI; Operating Temperature Min:0C;;RoHS Compliant: Yes |

| DM9102H | 制造商:DAVICOM 制造商全稱:DAVICOM 功能描述:Single Chip Fast Ethernet NIC Controller |

| DM9102HEP | 制造商:DAVICOM 制造商全稱:DAVICOM 功能描述:Single Chip Fast Ethernet NIC Controller |

| DM9103 | 制造商:DAVICOM 制造商全稱:DAVICOM 功能描述:10/100 Mbps 3-port Ethernet Switch Controller with PCI Interface |

| DM9103EP | 制造商:DAVICOM 制造商全稱:DAVICOM 功能描述:Three Port Ethernet Switch Controller with PCI Interface |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。