- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄378482 > CY28326OC (CYPRESS SEMICONDUCTOR CORP) FTG for VIA PT880 Serial Chipset PDF資料下載

參數(shù)資料

| 型號(hào): | CY28326OC |

| 廠商: | CYPRESS SEMICONDUCTOR CORP |

| 元件分類: | XO, clock |

| 英文描述: | FTG for VIA PT880 Serial Chipset |

| 中文描述: | 333.3 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO48 |

| 封裝: | SSOP-48 |

| 文件頁(yè)數(shù): | 6/23頁(yè) |

| 文件大小: | 288K |

| 代理商: | CY28326OC |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)當(dāng)前第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)

CY28326

Document #: 38-07616 Rev. *A

Page 6 of 23

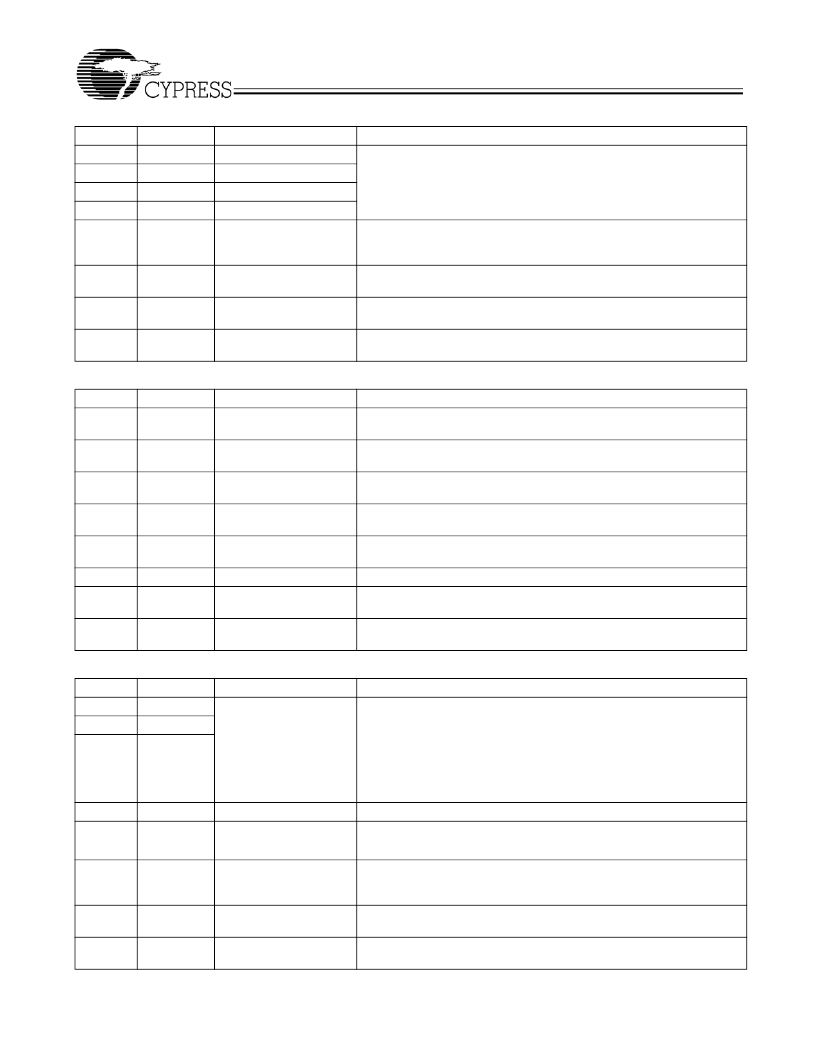

Byte 1: Control Register

Bit

7

6

5

4

3

@Pup

1

1

0

0

0

Name/Pin Affected

FS3

FS2

FS1

FS0

FS_Override/FS(D:A)

Description

SW frequency selection bits [3:0]. See table 2.

FS_Override

0 = Select operating frequency by FS(D:A) (HW Strapping) input bits,

1 = Select operating frequency by FSEL[3:0](SW Strapping) settings.

CPU[T/C]2

Powerdown/CPUSTP#

drive mode

0 = Driven in powerdown, 1 = Tri-state

CPU[T/C]1

Powerdown/CPUSTP#

drive mode

0 = Driven in powerdown, 1 = Tri-state

CPU[T/C]0

Powerdown/CPUSTP#

drive mode

0 = Driven in powerdown, 1 = Tri-state

2

0

CPU[T/C]2

1

0

CPU[T/C]1

0

0

CPU[T/C]0

Byte 2: Control Register

Bit

7

@Pup

0

Name/Pin Affected

PCIF[2:0]

Description

PCIF Clock Output Drive Strength

0 = Low drive strength, 1 = High drive strength

PCI Clock Output Drive Strength

0 = Low drive strength, 1 = High drive strength

AGP Clock Output Drive Strength

0 = Low drive strength, 1 = High drive strength

Don’t change, Default =0

6

0

PCI[6:0]

5

0

AGP[2:0]

4

0

Test bit

3

0

48 MHz, 24/48 MHz

48 MHz Clock Output Drive Strength

0 = Low drive strength, 1 = High drive strength

Reserved

REF Clock Output Drive Strength

0 = Low drive strength, 1 = High drive strength

Don’t change, Default =0

2

1

0

0

Reserved

REF[1:0]

0

0

Test bit

Byte 3: Control Register

Bit

7

6

5

@Pup

0

1

1

Name/Pin Affected

Spread Spectrum Sel

CPU

AGP

PCIF

PCI

Description

Spread Spectrum Selection

‘000’ = –1.25 ~ 0.25%

‘001’ = –1.0%

‘010’ = –0.75%

‘011’ = –0.5% (default)

‘100’ = ± 0.75%

‘101’ = ± 0.5%

‘110’ = ± 0.35%

‘111’ = ± 0.25%

AGP Skew control, relative to PCICLK

4

3

0

0

AGP_SKEW1

AGP_SKEW0

01 = –300ps

10 = +300ps

11 = +450ps

Spread Spectrum Enable/Disable Function

0 = Spread spectrum disable

1 = Spread spectrum enable

REF1 Output Enable

0 = Disabled, 1 = Enabled

REF0 Output Enable

0 = Disabled, 1 = Enabled

2

0

CPU,AGP,PCIF,PCI

1

1

REF1

0

1

REF0

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| CY28326OCT | FTG for VIA PT880 Serial Chipset |

| CY28326OXC | Single Pole Normally Open: 1-Form-A |

| CY28326OXCT | Single Pole Normally Open: 1-Form-A |

| CY28341-2 | Universal Clock Chip for VIA P4M/KT/KM400 DDR Systems |

| CY29962 | 2.5V/3.3V, 150-MHz Multi-Output Zero Delay Buffer |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| CY28326OCT | 制造商:CYPRESS 制造商全稱:Cypress Semiconductor 功能描述:FTG for VIA PT880 Serial Chipset |

| CY28326OXC | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| CY28326OXCT | 制造商:CYPRESS 制造商全稱:Cypress Semiconductor 功能描述:FTG for VIA PT880 Serial Chipset |

| CY28326SPC | 制造商:Cypress Semiconductor 功能描述: |

| CY28329 | 制造商:SPECTRALINEAR 制造商全稱:SPECTRALINEAR 功能描述:133 MHz Spread Spectrum Clock Synthesizer/Driver with Differential CPU Outputs |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。