- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄366628 > C9706AY ST92141 - 8/16 BIT MCU FOR 3-PHASE AC MOTOR CONTROL PDF資料下載

參數(shù)資料

| 型號: | C9706AY |

| 英文描述: | ST92141 - 8/16 BIT MCU FOR 3-PHASE AC MOTOR CONTROL |

| 中文描述: | CPU系統(tǒng)時鐘發(fā)生器| SSOP封裝| 48PIN |塑料 |

| 文件頁數(shù): | 12/19頁 |

| 文件大?。?/td> | 248K |

| 代理商: | C9706AY |

C9706

Clock Generator for VIA VT8371/Athlon (K7) Chipset Systems

Approved Product

Cypress Semiconductor Corporation

525 Los Coches St.

Milpitas, CA 95035. Tel: 408-263-6300, Fax: 408-263-6571

http://www.cypress.com

Document#: 38-07041 Rev. **

05/02/2001

Page 12 of 19

Maximum Ratings

Maximum Input Voltage Relative to VSS: VSS - 0.3V

Maximum Input Voltage Relative to VDD: VDD + 0.3V

Storage Temperature:

Operating Temperature:

Maximum ESD protection

Maximum Power Supply:

-65oC to + 150oC

0oC to +85oC

2000V

5.5V

This device contains circuitry to protect the inputs

against damage due to high static voltages or electric

field; however, precautions should be taken to avoid

application of any voltage higher than the maximum

rated voltages to this circuit. For proper operation, Vin

and Vout should be constrained to the range:

VSS<(Vin or Vout)<VDD

Unused inputs must always be tied to an appropriate

logic voltage level (either VSS or VDD).

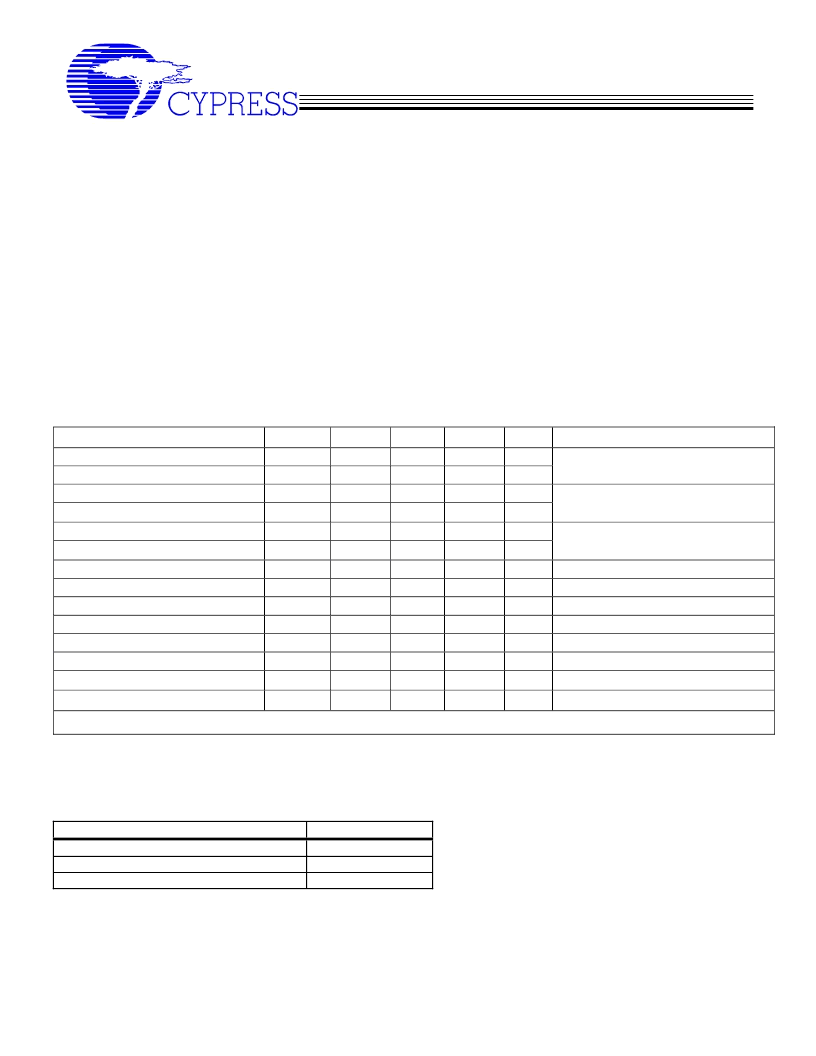

DC Parameters

Characteristic

Input Low Voltage

Input High Voltage

Input Low Current (@VIL = VSS)

Input High Current (@VIL =VDD)

Input Low Current (@VIL = VSS)

Input High Current (@VIL =VDD)

Tri-State leakage Current

Dynamic Supply Current

Input pin capacitance

Output pin capacitance

Pin inductance

Crystal pin capacitance

Crystal DC Bias Voltage

Crystal Startup time

Symbol

VIL2

VIH2

IIL

IIH

IIL

IIH

Ioz

Idd3.3V

Cin

Cout

Lpin

Cxtal

V

BIAS

Txs

Min

Typ

Max

Units

Vdc

Vdc

μA

μA

μA

μA

μA

mA

pF

pF

nH

pF

V

μ

S

Conditions

-

-

-

1.0

-

-5

5

-5

5

10

260

5

6

7

34

0.7Vdd

40

2.2

-66

Note 2

For internal Pull up resistors,

Notes 1,3

66

-

-

-

-

-

30

For internal Pull down resistors,

Notes 1,3

-

-

-

-

-

S(3:0) = 0111, Note 4

36

Measured from Pin to VSS. Note 5

0.3Vdd

-

Vdd/2

-

From Stable 3.3V power supply.

VDD = 3.3V

±

5

%, TA = 0o to +70oC

Note1:

Note2:

Note3:

Note4:

Note5:

Pull-down applicable to pin 25 (S3). Pull-up applicable to pins 2, 7, 8, 26, 41, 48.

Applicable to Sdata, and Sclk.

Although internal pull-down/up resistors have a typical value of 250K, this value may vary between 200K and 500K.

All outputs loaded as per table 5 below.

Although the device will reliably interface with crystals of a 15pF – 20pF C

L

range, it is optimized to interface with a typical C

L

= 16pF

crystal specifications.

Clock Name

CPU, REF

PCI, SDRAM

24MHz, 48MHz

Max Load (in pF)

20

30

15

Table 5

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| C9726AY | ST92141 - 8/16 BIT MCU FOR 3-PHASE AC MOTOR CONTROL |

| C9801CY | Hex buffer |

| C9805CYB | Quad line receivers |

| C9811X2AYB | Up to 5A ULDO linear regulator |

| C9812DYB | Up to 5A ULDO linear regulator |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| C9714 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:100 MHz Clock Generator with SSCG and Power Management for Mobile Application |

| C9714AT | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:100 MHz Clock Generator with SSCG and Power Management for Mobile Application |

| C9714AY | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:100 MHz Clock Generator with SSCG and Power Management for Mobile Application |

| C9716J | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:100 MHz Clock Generator with SSCG and Power Management for Mobile Application |

| C9716JT | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:100 MHz Clock Generator with SSCG and Power Management for Mobile Application |

發(fā)布緊急采購,3分鐘左右您將得到回復。