- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄210357 > BUS-65164-130K (DATA DEVICE CORP) 2 CHANNEL(S), 1M bps, MIL-STD-1553 CONTROLLER, CDFP70 PDF資料下載

參數(shù)資料

| 型號: | BUS-65164-130K |

| 廠商: | DATA DEVICE CORP |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | 2 CHANNEL(S), 1M bps, MIL-STD-1553 CONTROLLER, CDFP70 |

| 封裝: | 1.900 X 1 INCH, 0.215 INCH HEIGHT, FP-70 |

| 文件頁數(shù): | 37/40頁 |

| 文件大?。?/td> | 349K |

| 代理商: | BUS-65164-130K |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁當前第37頁第38頁第39頁第40頁

6

D00

D01

WC 0

WC 1

A0

A1

A2

A3

A4

A5

A6

A7

A8

A9

A10

4Kx1

PROM

SA 2

WC 2

WC 3

SA 3

SA 4

T/R

WC 4

SA 0

SA 1

A07

A10

A11

A08

A09

A12

D02

D03

D04

BUS-65153

"STIC"

A13

ILLEGAL

_______

BRO

A11

OE

__

D0

CS

__

Q

D

Q

state mode, based on broadcast, T/R bit, subaddress, and word

count requires an external latch to store the value of the word

count field. The word count must be latched after the address

lines A5...A1 are updated for the present command and before

these address lines are cleared to 00000 for the command word

transfer.

The word count address lines (A5...A1) are multiplexed internal-

ly between the latched word count field of the command word,

and the current word counter. While the signal INCMD is high

(logic 1) these address lines reflect the word count field of the

present command. While INCMD is low (logic 0) these signals

represent the value of the current word counter, which is cleared

to zero at the start of a message, and is incremented after each

data word transfer.

The output of the illegalization PROM may be latched using a

flip-flop and an AND gate (see FIGURE 2). The output signal

INCMD from the STIC is used as the clock enable input to the

flip-flop. The flip-flop is updated on every rising clock edge while

INCMD is high, and is not updated while INCMD is low. This

allows the output of the PROM to be updated on the last clock

edge before INCMD is asserted low. Once INCMD is asserted,

the clock enable input to the flip-flop is removed, thus preserving

the value of the latched illegal bit.

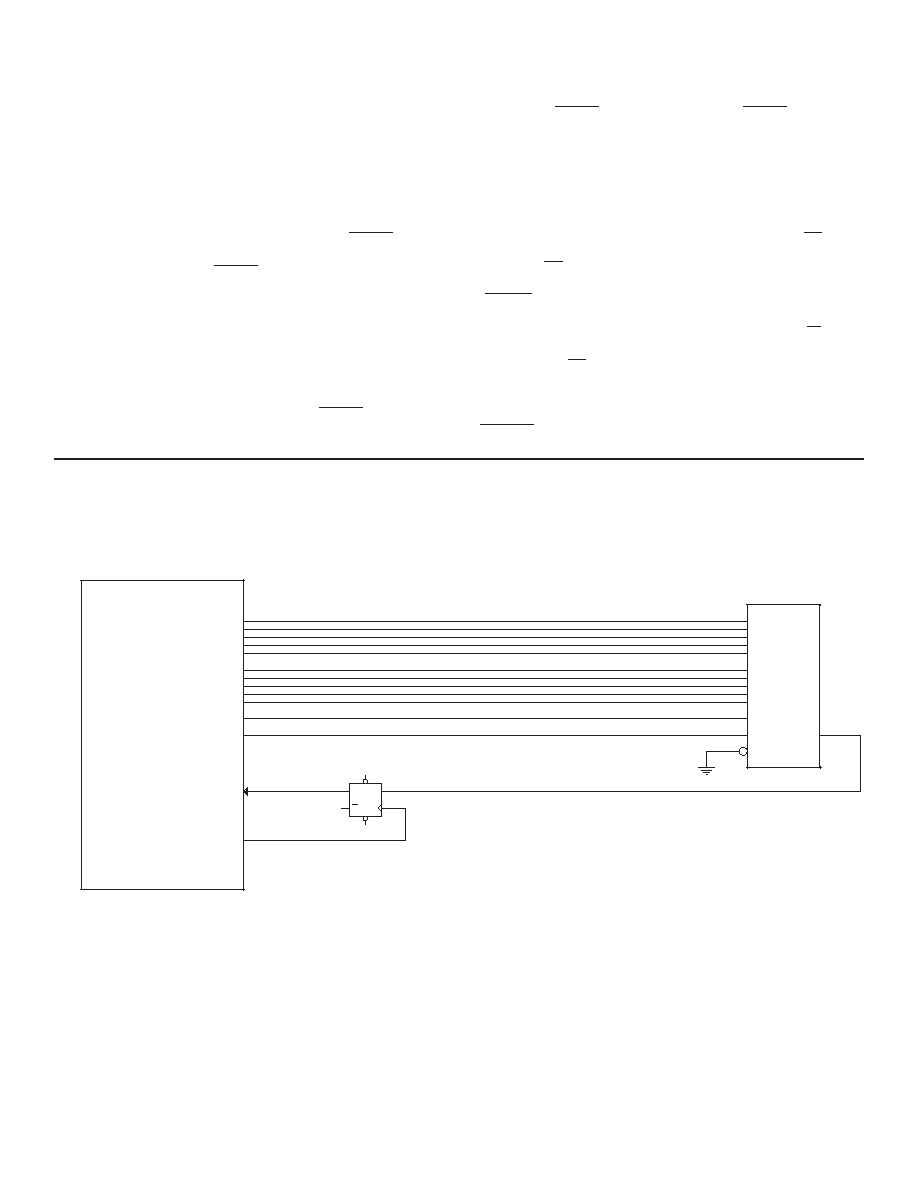

Illegalizing commands in the three-state mode of operation also

requires the use of a latch. The latch must be updated during a

word transfer since the address lines are normally in a high

impedance state. FIGURE 3 illustrates a method of latching the

output from the PROM using a flip-flop and the signal CS.

The signal CS is driven low during every word transfer. The only

word transfer that takes place before the illegal command input

(ILLCMD) input is sampled is the command word transfer. The

word count field of the command word may be obtained directly

from the lower 5 bits of the data bus. The subaddress, T/R, and

broadcast signals are available on address lines A07-A13. Note

that the signal CS will be asserted twice during a transfer in the

8-bit mode of operation. The word count field is located in the

lower byte, which is presented during the second byte transfer.

The second CS will, therefore, latch the appropriate value for

ILLEGAL.

FIGURE 3. BUS-65153 THREE-STATE ILLEGALIZATION

相關PDF資料 |

PDF描述 |

|---|---|

| BUS-65164-180K | 2 CHANNEL(S), 1M bps, MIL-STD-1553 CONTROLLER, CDFP70 |

| BU-61743F3-100W | 2 CHANNEL(S), 1M bps, MIL-STD-1553 CONTROLLER, CQFP72 |

| BU-61743F3-202L | 2 CHANNEL(S), 1M bps, MIL-STD-1553 CONTROLLER, CQFP72 |

| BU-61743F3-202W | 2 CHANNEL(S), 1M bps, MIL-STD-1553 CONTROLLER, CQFP72 |

| BU-61743F3-280L | 2 CHANNEL(S), 1M bps, MIL-STD-1553 CONTROLLER, CQFP72 |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| BU-S802 | 制造商:Fuji Electric 功能描述: |

| BU-S803 | 制造商:Fuji Electric 功能描述: |

| BUS98 | 制造商:ONSEMI 制造商全稱:ON Semiconductor 功能描述:SITCHMODE Series NPN Silicon Power Transistors |

| BUS98/D | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:SWITCHMODE? Series NPN Silicon Power Transistors |

| BUS98A | 制造商:ONSEMI 制造商全稱:ON Semiconductor 功能描述:SITCHMODE Series NPN Silicon Power Transistors |

發(fā)布緊急采購,3分鐘左右您將得到回復。