- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄210357 > BUS-65164-130K (DATA DEVICE CORP) 2 CHANNEL(S), 1M bps, MIL-STD-1553 CONTROLLER, CDFP70 PDF資料下載

參數(shù)資料

| 型號: | BUS-65164-130K |

| 廠商: | DATA DEVICE CORP |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | 2 CHANNEL(S), 1M bps, MIL-STD-1553 CONTROLLER, CDFP70 |

| 封裝: | 1.900 X 1 INCH, 0.215 INCH HEIGHT, FP-70 |

| 文件頁數(shù): | 14/40頁 |

| 文件大?。?/td> | 349K |

| 代理商: | BUS-65164-130K |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁當前第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁

21

DATA

MID-PARITY

t11

2

DATA

(PARITY ERROR)

PRESENT COMMAND

t3

t4

t12

t13

t14

WC

t5

t8

CWC=0

WC

t6

t7

t9

t10

MIN

5.95

500

5.87

MAX

6.26

6.245

45

t11(@12MHz)

t10

t11(@16MHz)

DESCRIPTION

MID-PARITY CROSSING OF DATA WORD WITH EVEN PARITY TO FALLING EDGE OF ME

STATUS INPUTS HOLD TIME

MID-PARITY CROSSING OF DATA WORD WITH EVEN PARITY TO FALLING EDGE OF ME

TYP

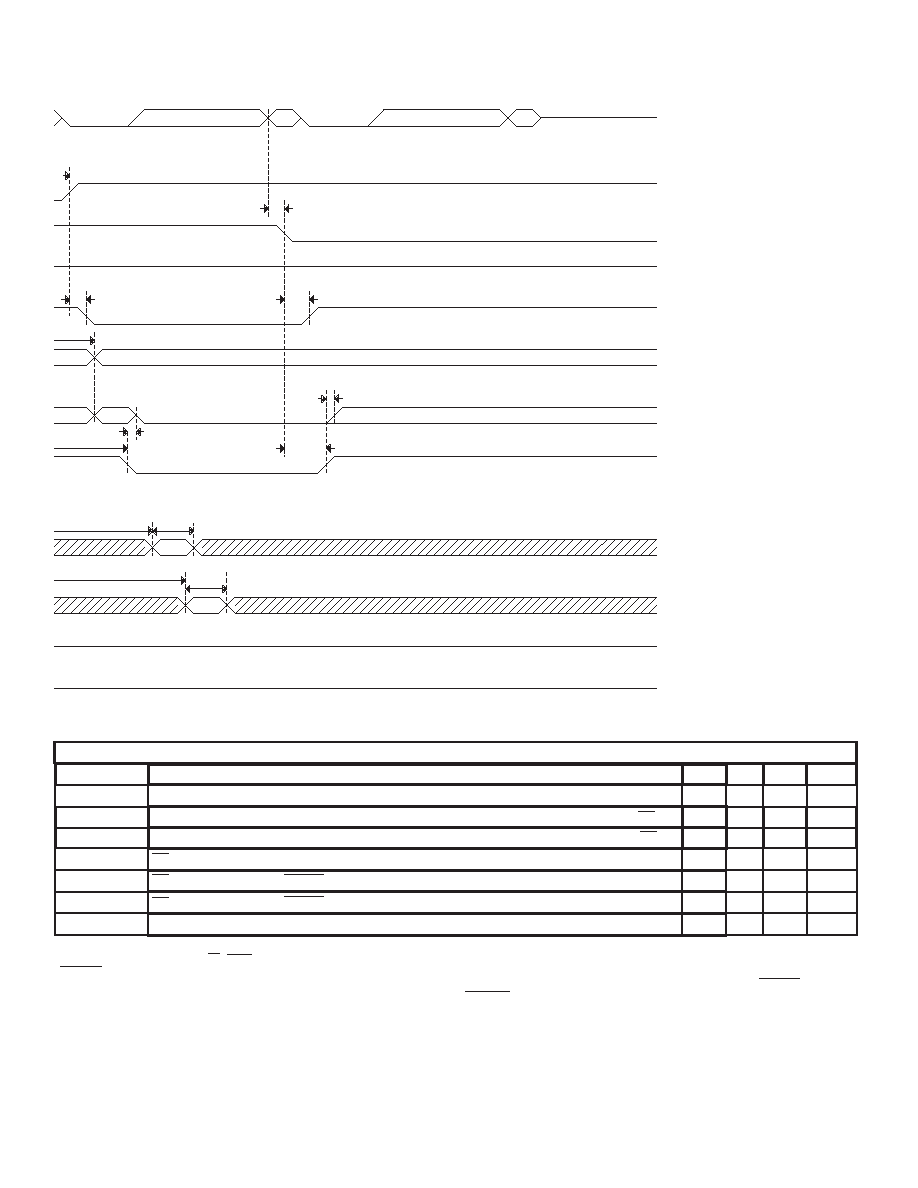

FIGURE 8. BC TO RT (RECEIVE) MESSAGE ERROR TIMING

UNITS

ms

ns

s

t12

ME FALLING EDGE TO A6 HIGH

ns

300

360

t13(@12MHz)

ME FALLING EDGE TO INCMD RISING EDGE

ns

220

280

t13(@16MHz)

ME FALLING EDGE TO INCMD RISING EDGE

ns

75

t14

INCMD RISING EDGE TO WORD COUNT VALID

Notes:

1)IF ADDR_ENA IS LOGIC “1”, CS, WRT, AND A13..A0 WILL BE IN A HIGH IMPEDANCE STATE EXCEPT FOR WHEN A WORD TRANSFER IS BEING PERFORMED

(DT_ACK = LOGIC “0”).

2)THE LEADING EDGE OF TIME REFERENCE t9 AND THE TRAILING EDGE OF TIME REFERENCE t6 IS DEFINED AS THE FALLING EDGE OF DT_REQ.

3)THE TRAILING EDGE OF REFERENCE t9 IS DEFINED AS THE RISING EDGE OF DT_REQ.

4)DATA TRANSFER CYCLE TIMING INFORMATION IS DESCRIBED IN OTHER FIGURES.

ns

SYMBOL

相關PDF資料 |

PDF描述 |

|---|---|

| BUS-65164-180K | 2 CHANNEL(S), 1M bps, MIL-STD-1553 CONTROLLER, CDFP70 |

| BU-61743F3-100W | 2 CHANNEL(S), 1M bps, MIL-STD-1553 CONTROLLER, CQFP72 |

| BU-61743F3-202L | 2 CHANNEL(S), 1M bps, MIL-STD-1553 CONTROLLER, CQFP72 |

| BU-61743F3-202W | 2 CHANNEL(S), 1M bps, MIL-STD-1553 CONTROLLER, CQFP72 |

| BU-61743F3-280L | 2 CHANNEL(S), 1M bps, MIL-STD-1553 CONTROLLER, CQFP72 |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| BU-S802 | 制造商:Fuji Electric 功能描述: |

| BU-S803 | 制造商:Fuji Electric 功能描述: |

| BUS98 | 制造商:ONSEMI 制造商全稱:ON Semiconductor 功能描述:SITCHMODE Series NPN Silicon Power Transistors |

| BUS98/D | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:SWITCHMODE? Series NPN Silicon Power Transistors |

| BUS98A | 制造商:ONSEMI 制造商全稱:ON Semiconductor 功能描述:SITCHMODE Series NPN Silicon Power Transistors |

發(fā)布緊急采購,3分鐘左右您將得到回復。