- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄369517 > BT457KPJ80 Video DAC with Color Palette (RAMDAC) PDF資料下載

參數(shù)資料

| 型號(hào): | BT457KPJ80 |

| 英文描述: | Video DAC with Color Palette (RAMDAC) |

| 中文描述: | 視頻DAC的調(diào)色板(的RAMDAC) |

| 文件頁數(shù): | 11/60頁 |

| 文件大小: | 647K |

| 代理商: | BT457KPJ80 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁當(dāng)前第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁

Bt457/Bt458

1.0 Circuit Description

125 MHz/135 MHz/165 MHz Monolithic CMOS 256 Color Palette RAMDAC

1.2 Pin Descriptions

L45801 Rev. N

Conexant

1-3

1.2 Pin Descriptions

Table 1-1. Pin Descriptions

(1 of 2)

Pin Name

Description

BLANK*

Composite blank control input (TTL compatible). A logical 0 drives the analog outputs to the blanking level, as

specified in

Table 1-5

. BLANK* is latched on the rising edge of LD*. When BLANK* is a logical 0, the pixel and

overlay inputs are ignored.

SYNC*

Composite sync control input (TTL compatible). A logical 0 on this input switches off a 40 IRE current source on

the IOG output (see

Figure 1-4

). SYNC* does not override any other control or data input, as illustrated in

Table 1-5

; therefore, it should be asserted only during the blanking interval. It is latched on the rising edge of

LD*.

If sync information is not generated on the IOG output, this pin should be connected to GND.

LD*

Load control input (TTL compatible). The P[7:0] {A

–

E}, OL[1,0] {A

–

E}, BLANK*, and SYNC* inputs are latched on

the rising edge of LD*. While LD* is either one fourth or one fifth the CLOCK rate, it can be phase independent of

the CLOCK and CLOCK* inputs. LD* can have any duty cycle within the limits specified in the AC Characteristics

section.

P[7:0]

{A

–

E}

Pixel select inputs (TTL compatible). These inputs are used to specify, on a pixel basis, which of the 256 entries

in the color palette RAM is used to provide color information. Either 4 or 5 consecutive pixels (up to 8 bits per

pixel) are input through this port. They are latched on the rising edge of LD*. Unused inputs should be connected

to GND.

The {A} pixel is output first, followed by the {B} pixel, then the {C} pixel, etc., until all 4 or 5 pixels have been

output, at which point the cycle repeats.

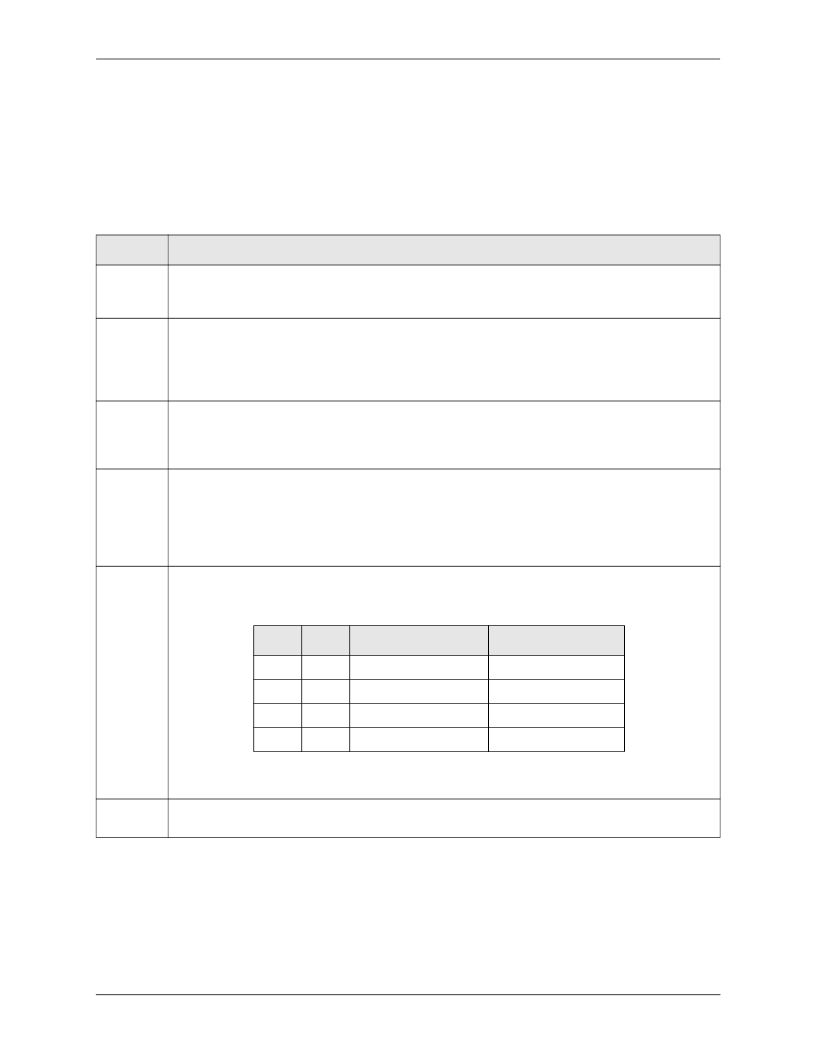

OL[1,0]

{A

–

E}

Overlay select inputs (TTL compatible). These control inputs are latched on the rising edge of LD*. In conjunction

with bit 6 of the command register, they specify which palette is to be used for color information, as follows:

When accessing the overlay palette, the P[7:0] {A

–

E} inputs are ignored. Overlay information bits (up to 2 bits per

pixel) for either 4 or 5 consecutive pixels are input through this port. Unused inputs should be connected to GND.

IOR, IOG,

IOB, IOUT

Red, green, and blue video current outputs. These high-impedance current sources can directly drive a doubly

terminated 75

coaxial cable (see

Figure 3-2

). The Bt457 outputs IOUT rather than IOR, IOG, and IOB.

OL1

OL0

CR6 = 1

CR6 = 0

0

0

Color Palette RAM

Overlay Color 0

0

1

Overlay Color 1

Overlay Color 1

1

0

Overlay Color 2

Overlay Color 2

1

1

Overlay Color 3

Overlay Color 3

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| BT8472EPF | Protocol Controller |

| BT8472KPF | Protocol Controller |

| BT8474EPF | Protocol Controller |

| BT848A | Single-Chip Video Capture for PCI |

| BT849A | Single-Chip Video Capture for PCI |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| BT458KG110 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Video DAC with Color Palette (RAMDAC) |

| BT458KG125 | 制造商: 功能描述: 制造商:undefined 功能描述: 制造商:BROOKTREE 功能描述: |

| BT458KG135 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Video DAC with Color Palette (RAMDAC) |

| BT458KG80 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Video DAC with Color Palette (RAMDAC) |

| BT458LG165 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Video DAC with Color Palette (RAMDAC) |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。