- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄366550 > AM79C972BKCW (ADVANCED MICRO DEVICES INC) PCnet⑩-FAST+ Enhanced 10/100 Mbps PCI Ethernet Controller with OnNow Support PDF資料下載

參數(shù)資料

| 型號: | AM79C972BKCW |

| 廠商: | ADVANCED MICRO DEVICES INC |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | PCnet⑩-FAST+ Enhanced 10/100 Mbps PCI Ethernet Controller with OnNow Support |

| 中文描述: | 5 CHANNEL(S), 100M bps, LOCAL AREA NETWORK CONTROLLER, PQFP16 |

| 封裝: | PLASTIC, QFP-160 |

| 文件頁數(shù): | 54/130頁 |

| 文件大小: | 1580K |

| 代理商: | AM79C972BKCW |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁當前第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁第113頁第114頁第115頁第116頁第117頁第118頁第119頁第120頁第121頁第122頁第123頁第124頁第125頁第126頁第127頁第128頁第129頁第130頁

54

Am79C972

.

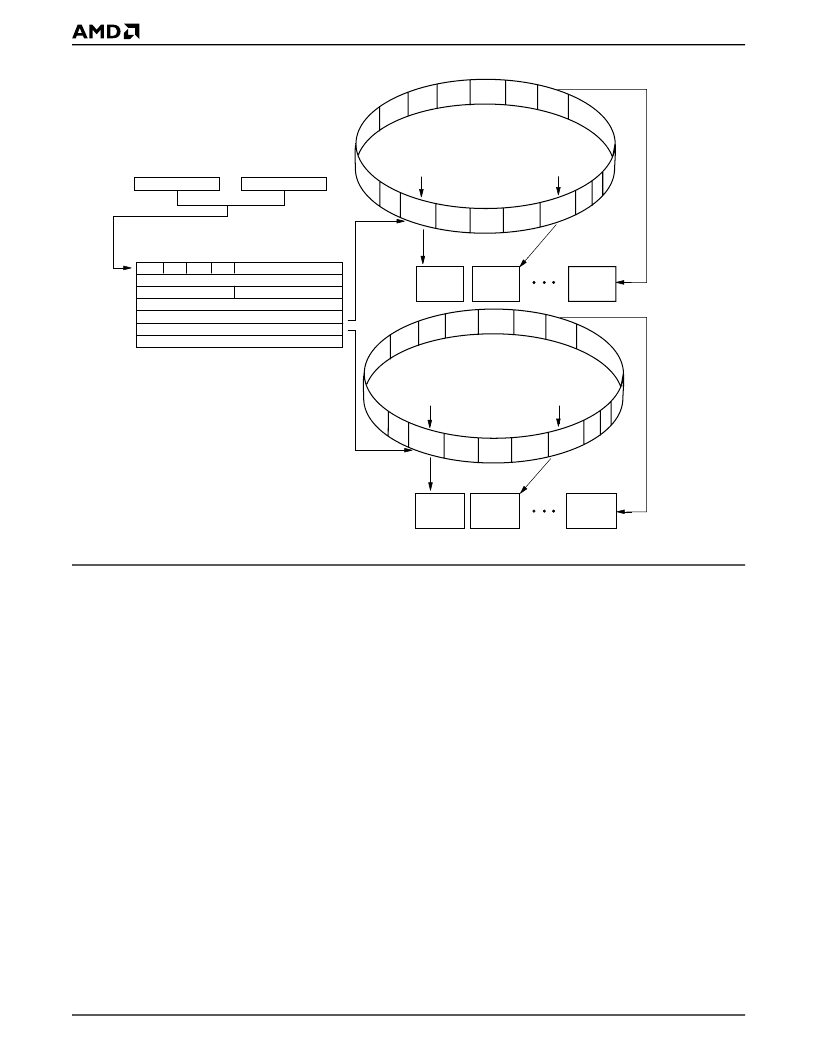

Figure 32.

32-Bit Software Model

If RXON is cleared to 0, the Am79C972 controller will

never poll RDTE locations.

In order to avoid missing frames, the system should

have at least one RDTE available. To minimize poll ac-

tivity, two RDTEs should be available. In this case, the

poll operation will only consist of the check of the status

of the current TDTE.

A typical transmit poll is the product of the following

conditions:

1. Am79C972 controller does not own the current

TDTE

and

TXDPOLL = 0 (CSR4, bit 12)

and

TXON = 1 (CSR0, bit 4)

and

the poll time has elapsed,

or

2. Am79C972 controller does not own the current

TDTE

and

TXDPOLL = 0

and

TXON = 1

and

a frame has just been received, or

3. Am79C972 controller does not own the current

TDTE

and

TXDPOLL = 0

and

TXON = 1

and

a frame has just been transmitted.

Setting the TDMD bit of CSR0 will cause the microcode

controller to exit the poll counting code and immedi-

ately perform a polling operation. If RDTE ownership

has not been previously established, then an RDTE

poll will be performed ahead of the TDTE poll. If the mi-

crocode is not executing the poll counting code when

the TDMD bit is set, then the demanded poll of the

TDTE will be delayed until the microcode returns to the

poll counting code.

The user may change the poll time value from the de-

fault of 65,536 clock periods by modifying the value in

the Polling Interval register (CSR47).

Transmit Descriptor Table Entry

If, after a Transmit Descriptor Table Entry (TDTE) ac-

cess, the Am79C972 controller finds that the OWN bit

of that TDTE is not set, the Am79C972 controller re-

sumes the poll time count and re-examines the same

TDTE at the next expiration of the poll time count.

If the OWN bit of the TDTE is set, but the Start of

Packet (STP) bit is not set, the Am79C972 controller

will immediately request the bus in order to clear the

OWN bit of this descriptor. (This condition would nor-

mally be found following a late collision (LCOL) or retry

(RTRY) error that occurred in the middle of a transmit

frame chain of buffers.) After resetting the OWN bit of

this descriptor, the Am79C972 controller will again im-

Initialization

Block

CSR1

IADR[15:0]

CSR2

IADR[31:16]

RMD

RMD

RMD

RMD

Rcv Descriptor

Ring

N

N

N

N

1st

desc.

start

2nd

desc.

start

RMD

TMD0

TMD1 TMD2

TMD3

Xmt Descriptor

Ring

M

M

M

M

1st

desc.

start

2nd

desc.

start

TMD0

Data

Buffer

N

Data

Buffer

1

Data

Buffer

2

Data

Buffer

M

Data

Buffer

2

Data

Buffer

1

PADR[31:0]

TLE

RES

RLE

RES

MODE

PADR[47:32]

RES

LADRF[31:0

LADRF[63:32]

RDRA[31:0]

TDRA[31:0]

Rcv

Buffers

Xmt

Buffers

21485C-35

相關PDF資料 |

PDF描述 |

|---|---|

| AM79C972BKIW | PCnet⑩-FAST+ Enhanced 10/100 Mbps PCI Ethernet Controller with OnNow Support |

| AM79C972BVCW | PCnet⑩-FAST+ Enhanced 10/100 Mbps PCI Ethernet Controller with OnNow Support |

| AM79C972 | PCnet⑩-FAST+ Enhanced 10/100 Mbps PCI Ethernet Controller with OnNow Support |

| AM79C972BVIW | PCnet⑩-FAST+ Enhanced 10/100 Mbps PCI Ethernet Controller with OnNow Support |

| AM79C974 | PCnetTM-SCSI Combination Ethernet and SCSI Controller for PCI Systems |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| AM79C972BKD/W | 制造商:Advanced Micro Devices 功能描述: |

| AM79C972BKD\\W | 制造商:Advanced Micro Devices 功能描述: |

| AM79C972BKD\W | 制造商:Advanced Micro Devices 功能描述: |

| AM79C972BKIW | 制造商:AMD 制造商全稱:Advanced Micro Devices 功能描述:PCnet⑩-FAST+ Enhanced 10/100 Mbps PCI Ethernet Controller with OnNow Support |

| AM79C972BVC | 制造商:Advanced Micro Devices 功能描述: |

發(fā)布緊急采購,3分鐘左右您將得到回復。