- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄366545 > AM5X86 (Advanced Micro Devices, Inc.) High-Performance Design On-Chip Integration Complete 32-Bit Architecture Micrprocessor(高性能單片32位微處理器) PDF資料下載

參數(shù)資料

| 型號: | AM5X86 |

| 廠商: | Advanced Micro Devices, Inc. |

| 英文描述: | High-Performance Design On-Chip Integration Complete 32-Bit Architecture Micrprocessor(高性能單片32位微處理器) |

| 中文描述: | 高性能設計的片上集成完整的32位架構Micrprocessor(高性能單片32位微處理器) |

| 文件頁數(shù): | 42/67頁 |

| 文件大小: | 1201K |

| 代理商: | AM5X86 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁當前第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁

42

Am5

X

86 Microprocessor

AMD

PRELIMINARY

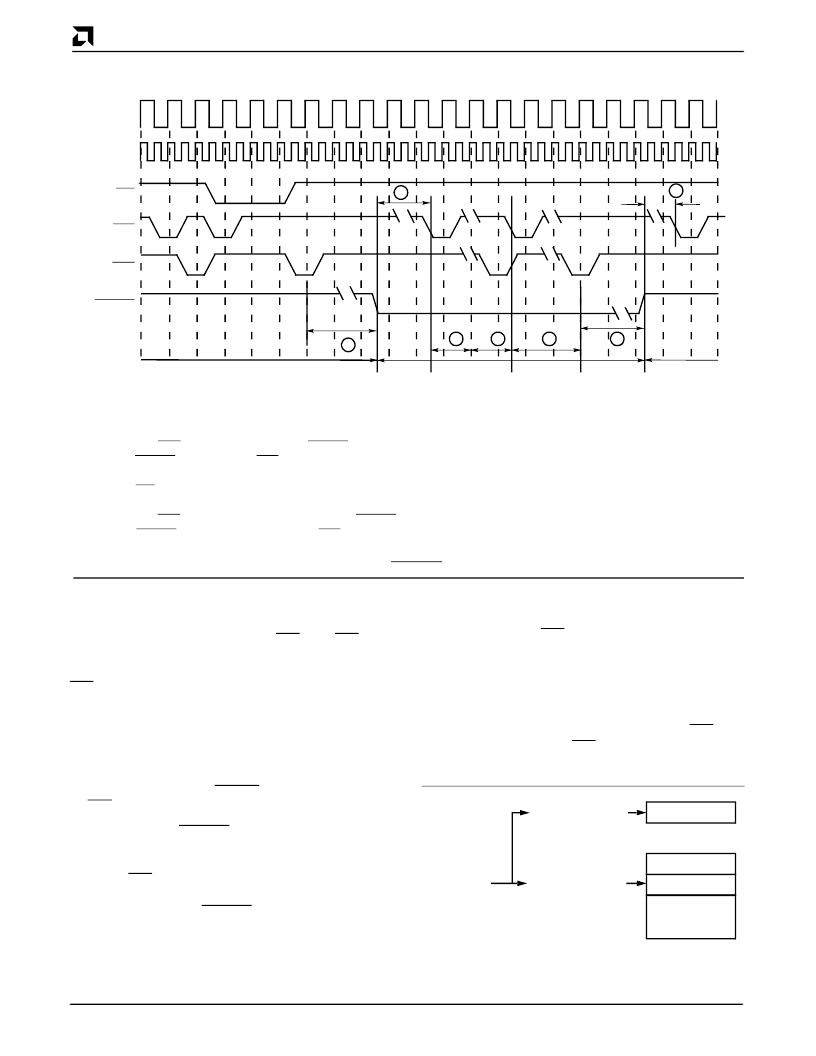

CLK

CLK2

SMI

SMIACT

ADS

RDY

T1

T2

Normal State

State

Save

SMM

Handler

State

Restore

Normal

State

E

Clock-Tripled CPU Clock-Quadrupled CPU

2 CLKs minimum

15 CLKs minimum

100 CLKs

User-determined

A: Last RDY from non-SMM transfer to SMIACT assertion

B: SMIACT assertion to first ADS for SMM state save

C: SMM state save (dependent on memory performance)

D: SMI handler

E: SMM state restore (dependent on memory performance) 180 CLKs

F: Last RDY from SMM transfer to deassertion of SMIACT

G: SMIACT deassertion of first non-SMM ADS

2 CLKs minimum

10 CLKs minimum

70 CLKs

User-determined

120 CLKs

2 CLKs minimum

20 CLKs minimum

2 CLKs minimum

20 CLKs minimum

Figure 25. SMIACT Timing

D

C

A

B

G

F

7.3.3

The CPU uses the SMRAM space for state save and

state restore operations during an SMI. The SMI han-

dler, which also resides in SMRAM, uses the SMRAM

space to store code, data, and stacks. In addition, the

SMI handler can use the SMRAM for system manage-

ment information such as the system configuration, con-

figuration of a powered-down device, and system

designer-specific information.

SMRAM

Note:

Access to SMRAM is through the CPU internal

cache. To ensure cache consistency and correct oper-

ation, always assert the FLUSH pin in the same clock

as SMI for systems using overlaid SMRAM.

The CPU asserts SMIACT to indicate to the memory

controller that it is operating in System Management

mode. The system logic should ensure that only the

CPU and SMI handler have access to this area. Alter-

nate bus masters or DMA devices trying to access the

SMRAM space when SMIACT is active should be di-

rected to system RAM in the respective area. The sys-

tem logic is minimally required to decode the physical

memory address range 38000h–3FFFFh as SMRAM

area. The CPU saves its state to the state save area

from 3FFFFh downward to 3FE00h. After saving its

state, the CPU jumps to the address location 38000h to

begin executing the SMI handler. The system logic can

choose to decode a larger area of SMRAM as needed.

The size of this SMRAM can be between 32 Kbytes and

4 Gbytes.The system logic should provide a manual

method for switching the SMRAM into system memory

space when the CPU is not in SMM. This enables ini-

tialization of the SMRAM space (i.e., loading SMI han-

dler) before executing the SMI handler during SMM (see

Figure 26).

SMRAM

System memory

accesses redirected

to SMRAM

System memory

accesses not

redirected to SMRAM

CPU

accesses to

system

address

space used

for loading

SMRAM

Normal

Memory

Space

Figure 26. Redirecting System Memory

Address to SMRAM

相關PDF資料 |

PDF描述 |

|---|---|

| AM6TW-2424D | 6 watt dc-dc converters |

| AM6TW-4803SH35 | 6 watt dc-dc converters |

| AM6TW-4805D | 6 watt dc-dc converters |

| AM6TW-4805DH35 | 6 watt dc-dc converters |

| AM6TW-4805S | 6 watt dc-dc converters |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| AM5X86-P75 | 制造商:Advanced Micro Devices 功能描述:Microprocessor, 32 Bit, 168 Pin, Ceramic, PGA |

| AM6 | 功能描述:按鈕開關 Push Button Oper, 30 mm,Non Ill. Mush., Mom., Blue RoHS:否 制造商:C&K Components 觸點形式:2 NC - 2 NO 開關功能:ON ? OFF 電流額定值:4 A 電壓額定值 AC:12 V to 250 V 電壓額定值 DC:12 V to 50 V 功率額定值: 安裝風格:Through Hole 照明:Illuminated 照明顏色:None IP 等級:IP 40 端接類型:Solder 觸點電鍍:Silver 執(zhí)行器:Square 蓋顏色: 封裝: 可燃性等級:UL 94 V-0 |

| AM-6 | 制造商:Greenlee Textron Inc 功能描述:MULTIMETER ANALOG 制造商:Greenlee Textron Inc 功能描述:MULTIMETER,ANALOG |

| AM60 | 制造商:Thomas & Betts 功能描述:60A ANGLE ADAPTER |

| AM600 | 制造商:EXTECH 制造商全稱:Extech Instruments Corporation. 功能描述:600A AC Analog Clamp Meter |

發(fā)布緊急采購,3分鐘左右您將得到回復。