- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄366544 > AM53C96KC (ADVANCED MICRO DEVICES INC) High Performance SCSI Controller PDF資料下載

參數(shù)資料

| 型號: | AM53C96KC |

| 廠商: | ADVANCED MICRO DEVICES INC |

| 元件分類: | 總線控制器 |

| 英文描述: | High Performance SCSI Controller |

| 中文描述: | SCSI BUS CONTROLLER, PQFP100 |

| 封裝: | 35 MM, CARRIER RING, PLASTIC, QFP-100 |

| 文件頁數(shù): | 30/63頁 |

| 文件大?。?/td> | 455K |

| 代理商: | AM53C96KC |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁當(dāng)前第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁

P R E L I M I N A R Y

AMD

30

Am53C94/Am53C96

FTMREG – Bit 1 – FIM – Forced Initiator Mode

The FIM bit when set forces the device into the initiator

mode. The device will then execute all initiator com-

mands irrespective of the SCSI bus status.

FTMREG – Bit 0 – FTM – Forced Target Mode

The FTM bit when set forces the device into the target

mode. The device will then execute all target commands

irrespective of the SCSI bus status.

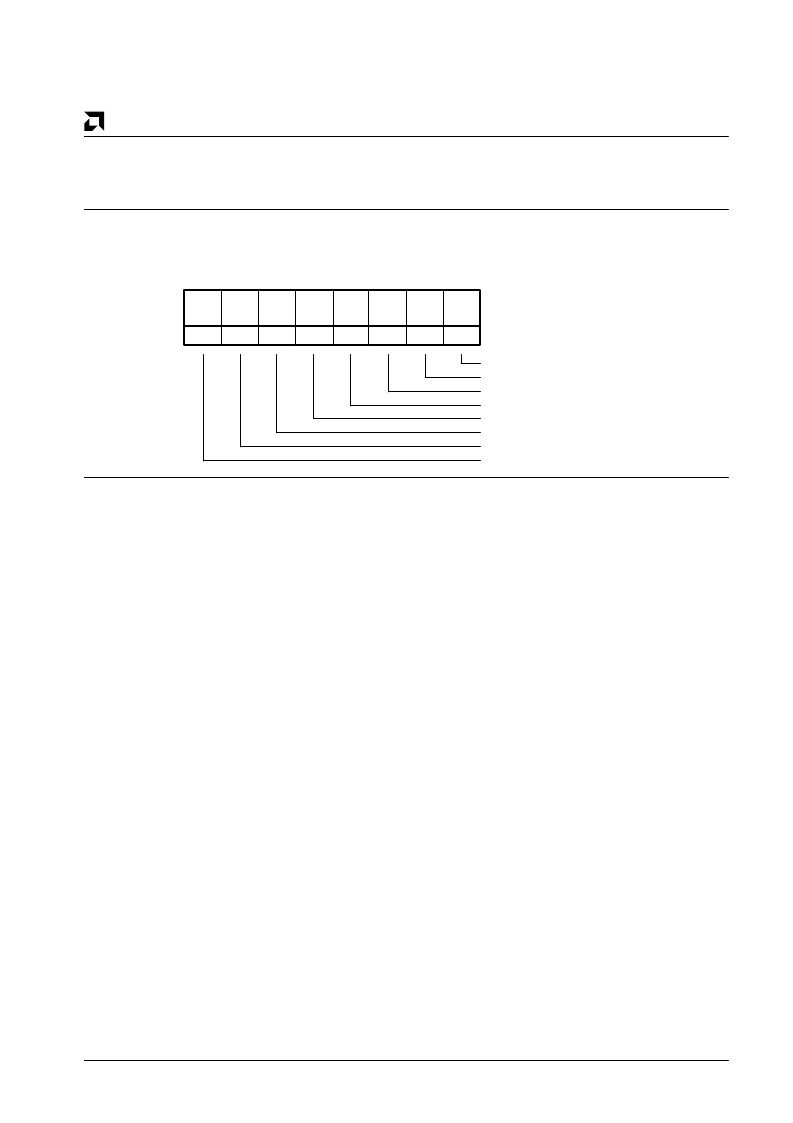

Control Register Two (0BH) Read/Write

Control Register Two

CNTLREG2

7

Address: 0B

H

Type: Read/Write

1

6

5

4

3

2

0

DAE

LSP

SBO

TSDR

S2FE

ACDPE

PGRP

PGDP

0

0

0

0

0

0

0

0

Latch SCSI Phase

Data Alignment Enable

Select Byte Order

Tri–State DMA Request

SCSI–2 Features Enable

Abort on Command/Data Parity Error

Pass Through/Generate Register Parity

Pass Through/Generate Data Parity

16506C-31

The Control Register 2 (CNTLREG2) sets up the device

with various operating parameters.

CNTLREG2 – Bit 7 – DAE – Data Alignment Enable

The DAE bit is used in the initiator Synchronous Data-In

phase only. When the DAE bit is set one byte is reserved

at the end of the FIFO when the phase changes to the

Synchronous Data-In phase. The contents of this byte

will become the lower byte of the DMA word (16-bit)

transfer to the memory, the upper byte being the first

byte of the first word received from the SCSI bus.

Note:

If an nterrupt s received for a misaligned boundary on a

phase change to synchronous data the following recov-

ery procedure may be followed. The host processor

should copy the byte at the start address in the host

memory to the Data Alignment Register 0FH (DALREG)

and then issue an information transfer command. The

first word the device will write to the memory (via DMA)

will consists of the ower byte from the DALREG and the

upper byte from the first byte received from the SCSI

bus.

The DAE bit must be set before the phase changes to

the Synchronous Data-In. The DAE bit is reset to zero by

a hard or soft reset or by writing the DALREG when in-

terrupted in the Synchronous Data-In phase.

CNTLREG2 – Bit 6 – LSP – Latch SCSI Phase

The LSP bit is used to enable or disable the latching of

the SCSI phase bits (MSG, C/D and I/O) in the Status

Register (STATREG) 04H.

When the LSP bit is set the phase bits STSTREG – Bits

2:0 are latched at the end of each command. This simpli-

fies software for stacked commands. When the LSP bit

is reset the phase bits STATREG – Bits 2:0 reflect the

actual state of the SCSI phase lines at any instant of

time. The LSP bit is reset by a hard or soft reset.

CNTLREG2 – Bit 5 – SBO – Select Byte Order

The SBO bit is used only when the BUSMD 1:0 = 10 to

enable or disable the byte control on the DMA interface.

When SBO is set and the BUSMD 1:0 = 10, the byte con-

trol inputs BHE and AS0 control the byte positions.

When SBO is reset the byte control inputs BHE and AS0

are ignored.

CNTLREG2 – Bit 4 – TSDR – Tri-State DMA

Request

The TSDR bit when set sends the DREQ output signal to

high impedance state and the device ignores all activity

on the DMA request (DREQ) input. This is useful for

wiring-OR several devices that share a common DMA

request line. When the TSDR bit is reset the DREQ

output is driven to TTL levels.

CNTLREG2 – Bit 3 – S2FE – SCSI–2 Features

Enable

The S2FE bit allows the device to recognize two SCSI-2

features. The two features are extended message fea-

ture and the Group 2 command recognition.

Extended Message Feature: When the S2FE bit is set

and the device is selected with attention, the device will

monitor the

ATN

signal at the end of the first message

byte. If the

ATN

signal is active, the device will request

two more message bytes before switching to the com-

mand phase. If the

ATN

signal is inactive the device will

switch to the command phase. When the S2FE bit is re-

set the device as a target will request a single message

byte. As an initiator, the device will abort the selection

sequence if the target does not switch to the command

phase after receiving a single message byte.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| AM53C96KCW | High Performance SCSI Controller |

| AM53C94 | Intergrated Optical Disk Controller |

| AM80C186 | Circular Connector; No. of Contacts:3; Series:MS27508; Body Material:Aluminum; Connecting Termination:Crimp; Connector Shell Size:12; Circular Contact Gender:Pin; Circular Shell Style:Box Mount Receptacle; Insert Arrangement:12-3 RoHS Compliant: No |

| AM80C286 | Circular Connector; No. of Contacts:10; Series:MS27508; Body Material:Aluminum; Connecting Termination:Crimp; Connector Shell Size:12; Circular Contact Gender:Socket; Circular Shell Style:Box Mount Receptacle RoHS Compliant: No |

| AM53C96 | Intergrated Optical Disk Controller |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| AM53C96KCW | 制造商:AMD 制造商全稱:Advanced Micro Devices 功能描述:High Performance SCSI Controller |

| AM53C974KC/W | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:SCSI Bus Interface/Controller |

| AM53CF94 | 制造商:AMD 制造商全稱:Advanced Micro Devices 功能描述:Enhanced SCSI-2 Controller (ESC) |

| AM53CF94/AM53CF96 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Am53CF94/Am53CF96 ? 572KB (PDF) Enhanced SCSI-2 Controller (ESC)? |

| AM53CF94JC | 制造商:AMD 制造商全稱:Advanced Micro Devices 功能描述:Enhanced SCSI-2 Controller (ESC) |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。