- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄25548 > 97ULP877AHLF-T (INTEGRATED DEVICE TECHNOLOGY INC) 97ULP SERIES, PLL BASED CLOCK DRIVER, 10 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PBGA52 PDF資料下載

參數(shù)資料

| 型號: | 97ULP877AHLF-T |

| 廠商: | INTEGRATED DEVICE TECHNOLOGY INC |

| 元件分類: | 時鐘及定時 |

| 英文描述: | 97ULP SERIES, PLL BASED CLOCK DRIVER, 10 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PBGA52 |

| 封裝: | ROHS COMPLIANT, PLASTIC, MO-205, MO-225, FBGA-52 |

| 文件頁數(shù): | 11/14頁 |

| 文件大小: | 176K |

| 代理商: | 97ULP877AHLF-T |

6

ICS97ULP877A

7116—03/27/07

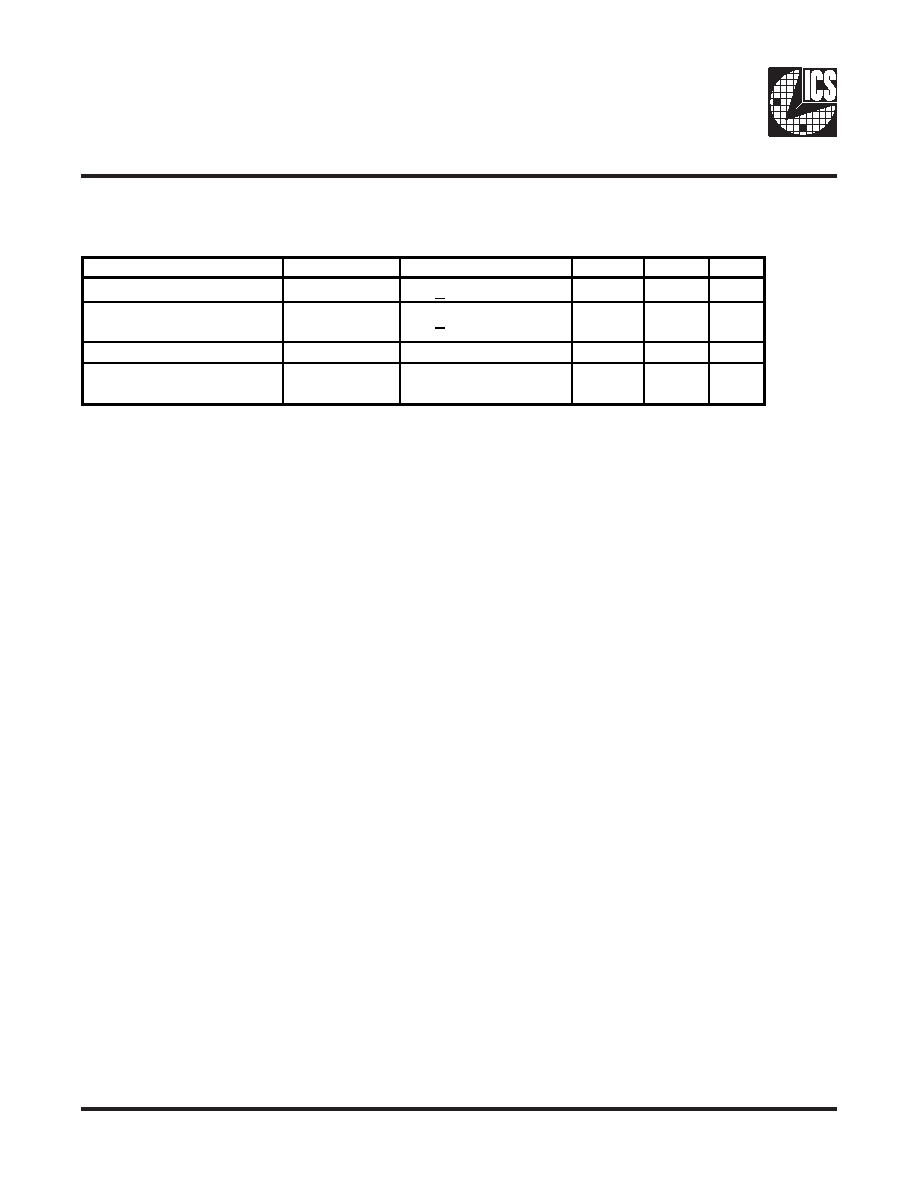

Timing R equirements

TA = 0 - 70°C Supply Voltage AVDD, VDDQ = 1.8 V +/- 0.1V (unless otherwise stated)

PARAMETER

SYMBOL

CONDITIONS

MIN

MAX

UNITS

Max clock frequency

freqop

1.8V+0.1V @ 25°C

95

410

MHz

Application Frequency

Range

freqApp

1.8V+0.1V @ 25°C

160

350

MHz

Input clock duty cycle

dtin

40

60

%

CLK stabilization

TSTAB

15

s

NOTE: The PLL must be able to handle spread spectrum induced skew.

NOTE: Operating clock frequency indicates a range over which the PLL must be able to lock, but in which it is not

required to meet the other timing parameters. (Used for low speed system debug.)

NOTE: Application clock frequency indicates a range over which the PLL must meet all timing parameters.

NOTE: Stabilization time is the time required for the integrated PLL circuit to obtain phase lock of its feedback

signal to its reference signal, within the value specificied by the Static Phase Offset (

t( ), after power-up. During

normal operation, the stabilization time is also the time required for the integrated PLL circuit to obtain phase lock

of its feedback signal to its reference signal when CK and CK go to a logic low state, enter the power-down mode

and later return to active operation. CK and CK may be left floating after they have been driven low for one

complete clock cycle.

相關PDF資料 |

PDF描述 |

|---|---|

| 97ULP877BHLF-T | 97ULP SERIES, PLL BASED CLOCK DRIVER, 10 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PBGA52 |

| 97ULP877BHLF | 97ULP SERIES, PLL BASED CLOCK DRIVER, 10 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PBGA52 |

| 97ULP877BKLF | 97ULP SERIES, PLL BASED CLOCK DRIVER, 10 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PQCC40 |

| 97ULP877BH | 97ULP SERIES, PLL BASED CLOCK DRIVER, 10 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PBGA52 |

| 97ULPA877AHLF-T | 97ULP SERIES, PLL BASED CLOCK DRIVER, 10 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PBGA52 |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| 97ULP877BHLF | 功能描述:時鐘驅動器及分配 RoHS:否 制造商:Micrel 乘法/除法因子:1:4 輸出類型:Differential 最大輸出頻率:4.2 GHz 電源電壓-最大: 電源電壓-最小:5 V 最大工作溫度:+ 85 C 封裝 / 箱體:SOIC-8 封裝:Reel |

| 97ULP877BHLFT | 功能描述:時鐘驅動器及分配 RoHS:否 制造商:Micrel 乘法/除法因子:1:4 輸出類型:Differential 最大輸出頻率:4.2 GHz 電源電壓-最大: 電源電壓-最小:5 V 最大工作溫度:+ 85 C 封裝 / 箱體:SOIC-8 封裝:Reel |

| 97ULP877BKLF/W | 制造商:Integrated Device Technology Inc 功能描述:ZERO DLY PLL CLOCK DRVR SGL 95MHZ TO 410MHZ 40PIN VFQFPN - Tape and Reel |

| 97ULP878AH | 制造商:Integrated Device Technology Inc 功能描述:97ULP878AH - Trays |

| 97ULP878AHLF | 制造商:Integrated Device Technology Inc 功能描述:97ULP878AHLF - Trays |

發(fā)布緊急采購,3分鐘左右您將得到回復。