- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄378216 > 82596DX (Intel Corp.) HIGH-PERFORMANCE 32-BIT LOCAL AREA NETWORK COPROCESSOR PDF資料下載

參數(shù)資料

| 型號(hào): | 82596DX |

| 廠商: | Intel Corp. |

| 英文描述: | HIGH-PERFORMANCE 32-BIT LOCAL AREA NETWORK COPROCESSOR |

| 中文描述: | 高性能的32位局域網(wǎng)協(xié)處理器 |

| 文件頁(yè)數(shù): | 11/77頁(yè) |

| 文件大?。?/td> | 787K |

| 代理商: | 82596DX |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)當(dāng)前第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)第75頁(yè)第76頁(yè)第77頁(yè)

82596DX/SX

PIN DESCRIPTIONS

(Continued)

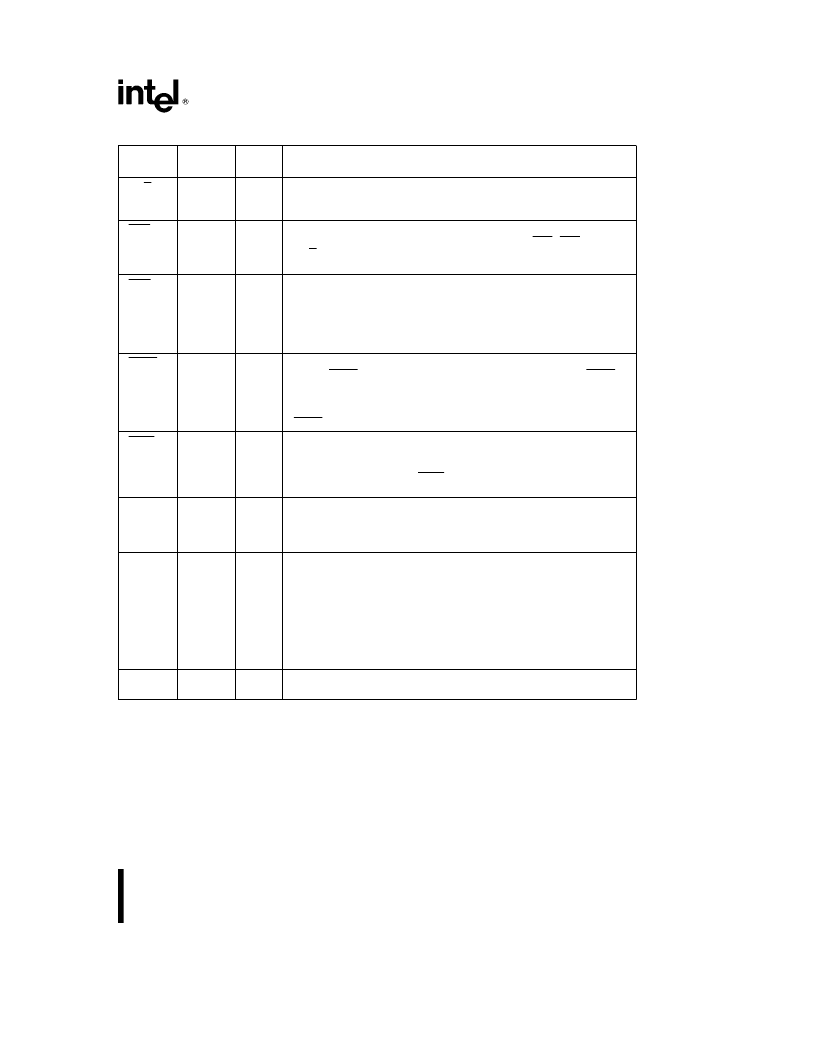

Symbol

PQFP

Pin No.

Type

Name and Function

W/R

120

O

WRITE/READ.

This dual-function pin is used to distinguish Write and

Read cycles. This line is floated after a Reset or when the bus is not

acquired.

ADS

124

O

ADDRESS STATUS.

This tri-state pin is used by the 82596 to indicate

that a valid bus cycle has begun and that A31–A2, BE3–BE0, and

W/R are being driven. It is asserted during t1 bus states. This line is

floated after a Reset or when the bus is not acquired.

RDY

130

I

READY.

Active low. This signal is the acknowledgment from

addressed memory that the transfer cycle can be completed. When

high, it causes wait states to be inserted. It is ignored at the end of the

first clock of the bus cycle’s data cycle. This active-low signal does not

have an internal pull-up resistor. This signal must meet the setup and

hold times to operate correctly.

LOCK

126

O

LOCK.

This tri-state pin is used to distinguish locked and unlocked bus

cycles. LOCK generates a semaphore handshake to the CPU. LOCK

can be active for several memory cycles, it goes active during the first

locked memory cycle (t1) and goes inactive at the last locked cycle

(t2). This line is floated after a Reset or when the bus is not acquired.

LOCK can be disabled via the sysbus byte in software.

BS16

129

I

BUS SIZE.

This signal allows the 82596DX to work with either 16- or

32-bit bytes. This signal is static and should be tied high for 32-bit

operation or low for 16-bit operation. In Little Endian mode the D0–

D15 lines are driven when BS16 is inserted, in Big Endian mode the

D16–D31 lines are driven.

HOLD

123

O

HOLD.

The HOLD signal is active high, the 82596 uses it to request

local bus mastership. In normal operation HOLD goes inactive before

HLDA. The 82596 can be forced off the bus by deasserting HLDA or if

the bus throttle timers expire.

HLDA

118

I

HOLD ACKNOWLEDGE.

The HLDA signal is active high, it indicates

that bus mastership has been given to the 82596. HLDA is internally

synchronized; after HOLD is detected low, the CPU drives HLDA low.

NOTE

Do not connect HLDA to V

CC

Dit will cause a deadlock. A user wanting

to give the 82596 permanent access to the bus should connect HLDA

to HOLD. If HLDA goes inactive before HOLD, the 82596 will release

the bus (by deasserting HOLD) within a specified number of system

clocks.

BREQ

115

I

BUS REQUEST.

This signal, when configured to an externally

activated mode, is used to trigger the bus throttle timers.

11

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| 82596SX | HIGH-PERFORMANCE 32-BIT LOCAL AREA NETWORK COPROCESSOR |

| 82596CA | HIGH-PERFORMANCE 32-BIT LOCAL AREA NETWORK COPROCESSOR |

| 8261SHAKE22 | Alternate Action and Momentary Pushbutton Switches |

| 8261SHAKE223 | Alternate Action and Momentary Pushbutton Switches |

| 8261SHAPE22 | Alternate Action and Momentary Pushbutton Switches |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| 82596SX | 制造商:INTEL 制造商全稱:Intel Corporation 功能描述:HIGH-PERFORMANCE 32-BIT LOCAL AREA NETWORK COPROCESSOR |

| 82598 | 制造商:INTEL 制造商全稱:Intel Corporation 功能描述:10 GbE Controller |

| 825981-000 | 功能描述:環(huán)形MIL規(guī)格應(yīng)變消除裝置與適配器 TXR18AB00C2008AI RoHS:否 制造商:Amphenol Industrial 產(chǎn)品:Cable Clamps 類型:Bushing Cable Clamps MIL 類型:MIL-DTL-5015 系列:97 外殼大小:16S, 16 匹配樣式:Threaded 主體材料:Aluminum Alloy 主體類型:Straight |

| 82-5988-1000 | 功能描述:RF 連接器 N RIGHT ANGLE CRIMP PLUG RoHS:否 制造商:Bomar Interconnect 產(chǎn)品:Connectors 射頻系列:BNC 型式:Jack (Female) 極性: 觸點(diǎn)電鍍:Gold 阻抗: 端接類型:Solder 主體類型:Straight Bulkhead 電纜類型: |

| 82599_10 | 制造商:INTEL 制造商全稱:Intel Corporation 功能描述:Transforming the data center through a reliable and unified 10GbE network |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。