- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄378216 > 82546EB (Intel Corp.) Dual Port Gigabit Ethernet Controller PDF資料下載

參數(shù)資料

| 型號: | 82546EB |

| 廠商: | Intel Corp. |

| 英文描述: | Dual Port Gigabit Ethernet Controller |

| 中文描述: | 雙端口千兆以太網(wǎng)控制器 |

| 文件頁數(shù): | 16/47頁 |

| 文件大小: | 281K |

| 代理商: | 82546EB |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁當(dāng)前第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁

82546EB

— Networking Silicon

10

Datasheet

3.2.2

Arbitration Signals

3.2.3

Interrupt Signals

3.2.4

System Signals

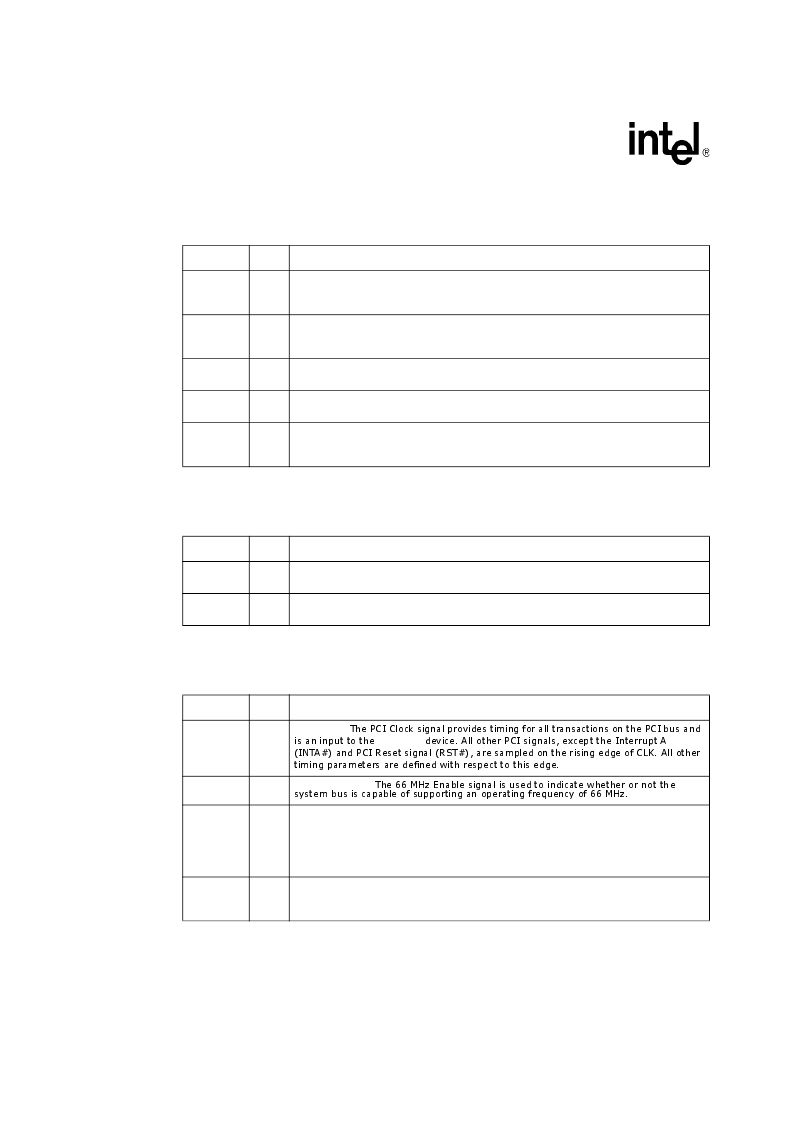

Symbol

Type

Name and Function

REQ64#

TS

Request Transfer.

The Request Transfer signal is generated by the current initiator

indicating its desire to perform a 64-bit transfer. REQ64# has the same timing as the

Frame signal.

ACK64#

TS

Acknowledge Transfer.

The Acknowledge Transfer signal is generated by the currently

addressed target in response to the REQ64# assertion by the initiator. ACK64# has the

same timing as the Device Select signal.

REQ#

TS

Request Bus.

The Request Bus signal is used to request control of the bus from the

arbiter. This signal is point-to-point.

GNT#

I

Grant Bus.

The Grant Bus signal notifies the

82546EB

that bus access has been

granted. This is a point-to-point signal.

LOCK#

I

Lock Bus.

The Lock Bus signal is asserted by an initiator to require sole access to a

target memory device during two or more separate transfers. The

82546EB

device

does not implement bus locking.

Symbol

Type

Name and Function

INTA#

TS

Interrupt A.

Interrupt A is used to request an interrupt by port 1 of the. It is an active

low, level-triggered interrupt signal.

INTB#

TS

Interrupt B.

Interrupt B is used to request an interrupt by port 2 of the 82546EB. It is an

active low, level-triggered interrupt signal.

Symbol

Type

Name and Function

CLK

I

PCI Clock.

The PCI Clock signal provides timing for all transactions on the PCI bus and

is an input to the

82546EB

device. All other PCI signals, except the Interrupt A

(INTA#) and PCI Reset signal (RST#), are sampled on the rising edge of CLK. All other

timing parameters are defined with respect to this edge.

M66EN

I

66 MHz Enable.

The 66 MHz Enable signal is used to indicate whether or not the

system bus is capable of supporting an operating frequency of 66 MHz.

RST#

I

PCI Reset.

When the PCI Reset signal is asserted, all PCI output signals, except the

Power Management Event signal (PME#), are floated and all input signals are ignored.

The PME# context is preserved, depending on power management settings.

Most of the internal state of the

82546EB

is reset on the de-assertion (rising edge) of

RST#.

LAN_

PWR_

GOOD

I

Power Good (Power-on Reset).

The Power Good signal is used to indicate that stable

power is available for the

82546EB

. When the signal is low, the

82546EB

holds itself in

reset state and floats all PCI signals.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| 8254 | PROGRAMMABLE INTERVAL TIMER |

| 82555 | 10/100 Mbps LAN physical layer interface |

| 82557 | Fast Ethernet PCI Bus Controller(快速以太網(wǎng) PCI總線控制器) |

| 82559 | Fast Ethernet Multifunction PCI/CARD bus controller(快速以太網(wǎng)多功能PCI/CARD 總線控制器) |

| 8255A-5 | PROGRAMMABLE PERIPHEAL INTERFACE |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| 82546GB | 制造商:INT 功能描述: 制造商:undefined 功能描述: |

| 825470 | 功能描述:UC-EMLP (27X12 5) YE 制造商:phoenix contact 系列:* 零件狀態(tài):有效 標(biāo)準(zhǔn)包裝:10 |

| 82547-00000 | 制造商:3M Electronic Products Division 功能描述:ADAM ref. traded PUR |

| 825479-2 | 制造商:TE Connectivity 功能描述:MOD II VERT.MNT MAL - Bulk |

| 825479-3 | 制造商:TE Connectivity 功能描述:MOD II VERT.MNT MAL - Bulk |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。