- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄1887 > 73S1217F-68MR/F/PE (Maxim Integrated Products)IC SOC SMART CARD READER 68QFN PDF資料下載

參數(shù)資料

| 型號(hào): | 73S1217F-68MR/F/PE |

| 廠商: | Maxim Integrated Products |

| 文件頁(yè)數(shù): | 124/140頁(yè) |

| 文件大小: | 0K |

| 描述: | IC SOC SMART CARD READER 68QFN |

| 標(biāo)準(zhǔn)包裝: | 2,500 |

| 系列: | * |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)第75頁(yè)第76頁(yè)第77頁(yè)第78頁(yè)第79頁(yè)第80頁(yè)第81頁(yè)第82頁(yè)第83頁(yè)第84頁(yè)第85頁(yè)第86頁(yè)第87頁(yè)第88頁(yè)第89頁(yè)第90頁(yè)第91頁(yè)第92頁(yè)第93頁(yè)第94頁(yè)第95頁(yè)第96頁(yè)第97頁(yè)第98頁(yè)第99頁(yè)第100頁(yè)第101頁(yè)第102頁(yè)第103頁(yè)第104頁(yè)第105頁(yè)第106頁(yè)第107頁(yè)第108頁(yè)第109頁(yè)第110頁(yè)第111頁(yè)第112頁(yè)第113頁(yè)第114頁(yè)第115頁(yè)第116頁(yè)第117頁(yè)第118頁(yè)第119頁(yè)第120頁(yè)第121頁(yè)第122頁(yè)第123頁(yè)當(dāng)前第124頁(yè)第125頁(yè)第126頁(yè)第127頁(yè)第128頁(yè)第129頁(yè)第130頁(yè)第131頁(yè)第132頁(yè)第133頁(yè)第134頁(yè)第135頁(yè)第136頁(yè)第137頁(yè)第138頁(yè)第139頁(yè)第140頁(yè)

73S1217F Data Sheet

DS_1217F_002

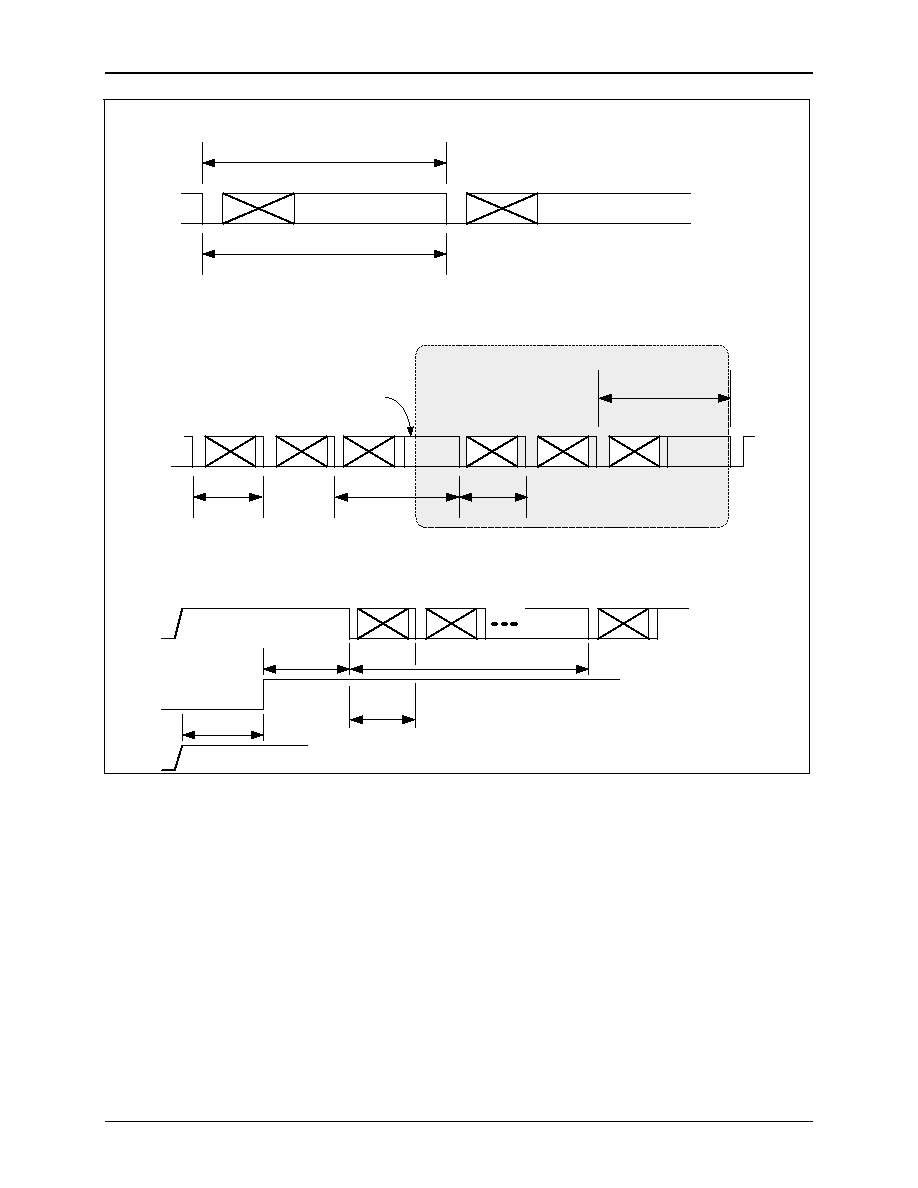

> EGT

< WWT

CHAR 1

CHAR 2

CHAR

N+1

CHAR

N+2

CHAR

N+3

BLOCK1

BLOCK2

> BWT

< CWT

RECEPTION

TRANSMISSION

T = 1 Mode

CHAR 1

CHAR 2

CHAR N

RST

TSTO(7:0)

ATRTO(15:0)

VCC_OK

RLen(7:0)

CHAR 1

CHAR 2

CHAR N

ATR Timing Parameters

IWT(15:0)

BGT(4:0)

TX

T = 0 Mode

IO

EGT

(By seting Last_TXByte and

TX/RXB=0 during CHAR N,

RX mode will start after last

TX byte)

WWT is set by the value in the BWT registers.

Figure 21: Guard, Block, Wait and ATR Time Definitions

1.7.17.4

Bypass Mode

It is possible to bypass the smart card UART in order for the firmware to support non-T=0/T=1 smart

cards. This is called Bypass mode. In this mode the embedded firmware will communicate directly with

the selected smart card and drive I/O during transmit and read I/O during receive in order to communicate

with the smart card. In this mode, ATR processing is under firmware control. The firmware must

sequence the interface signals as required. Firmware must perform TS processing, parity checking,

break generation and CRC/LRC calculation (if required).

1.7.17.5

Synchronous Operation Mode

The 73S1217F supports synchronous operation. When sync mode is selected for either interface, the

obtain the desired sync CLK rate. There is only one ETU counter and therefore, in sync mode, the

interface must be selected to obtain a smart card clock signal. In sync mode, input data is sampled on

the rise of CLK, and output data is changed on the fall of CLK.

Special Notes Regarding Synchronous Mode Operation

84

Rev. 1.2

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| 73S8010C-ILR/F | IC SMART CARD INTERFACE 28-SOIC |

| 73S8010R-ILR/F | IC SMART CARD INTERFACE 28-SOIC |

| 73S8014R-IL/F | IC SMART CARD 7816 EMV 20-SOIC |

| 73S8014RN-ILR/F | IC SMART CARD 7816 EMV 20-SOIC |

| 73S8023C-IMR/F | IC SMART CARD INTERFACE 32-QFN |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| 73S1217F-EB | 功能描述:開(kāi)發(fā)板和工具包 - 8051 73S1217F Eval Brd (Usb Cable, Doc. Cd) RoHS:否 制造商:Silicon Labs 產(chǎn)品:Development Kits 工具用于評(píng)估:C8051F960, Si7005 核心: 接口類型:USB 工作電源電壓: |

| 73S1217F-EB-Lite | 功能描述:開(kāi)發(fā)板和工具包 - 8051 73S1217F EVB Lite w/Plug & Play/Usb RoHS:否 制造商:Silicon Labs 產(chǎn)品:Development Kits 工具用于評(píng)估:C8051F960, Si7005 核心: 接口類型:USB 工作電源電壓: |

| 73S1217F-IMR/F | 制造商:TERIDIAN 制造商全稱:TERIDIAN 功能描述:Bus-Powered 80515 System-on-Chip with USB, ISO 7816 / EMV, PINpad and More |

| 73S13B | 制造商:QUARTZCOM 制造商全稱:QUARTZCOM the communications company 功能描述:-20 ~ +70 °C commercia l application -30 ~ +75 °C on request |

| 73S5040G01X0A | 制造商:NEX Computers 功能描述:INTEL 40GB SSD - Bulk |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。