- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄293971 > 5962D0053605QYX 512K X 8 STANDARD SRAM, 20 ns, CDFP36 PDF資料下載

參數(shù)資料

| 型號(hào): | 5962D0053605QYX |

| 元件分類: | SRAM |

| 英文描述: | 512K X 8 STANDARD SRAM, 20 ns, CDFP36 |

| 封裝: | CERAMIC, DFP-36 |

| 文件頁(yè)數(shù): | 13/16頁(yè) |

| 文件大小: | 138K |

| 代理商: | 5962D0053605QYX |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)當(dāng)前第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)

6

{

}

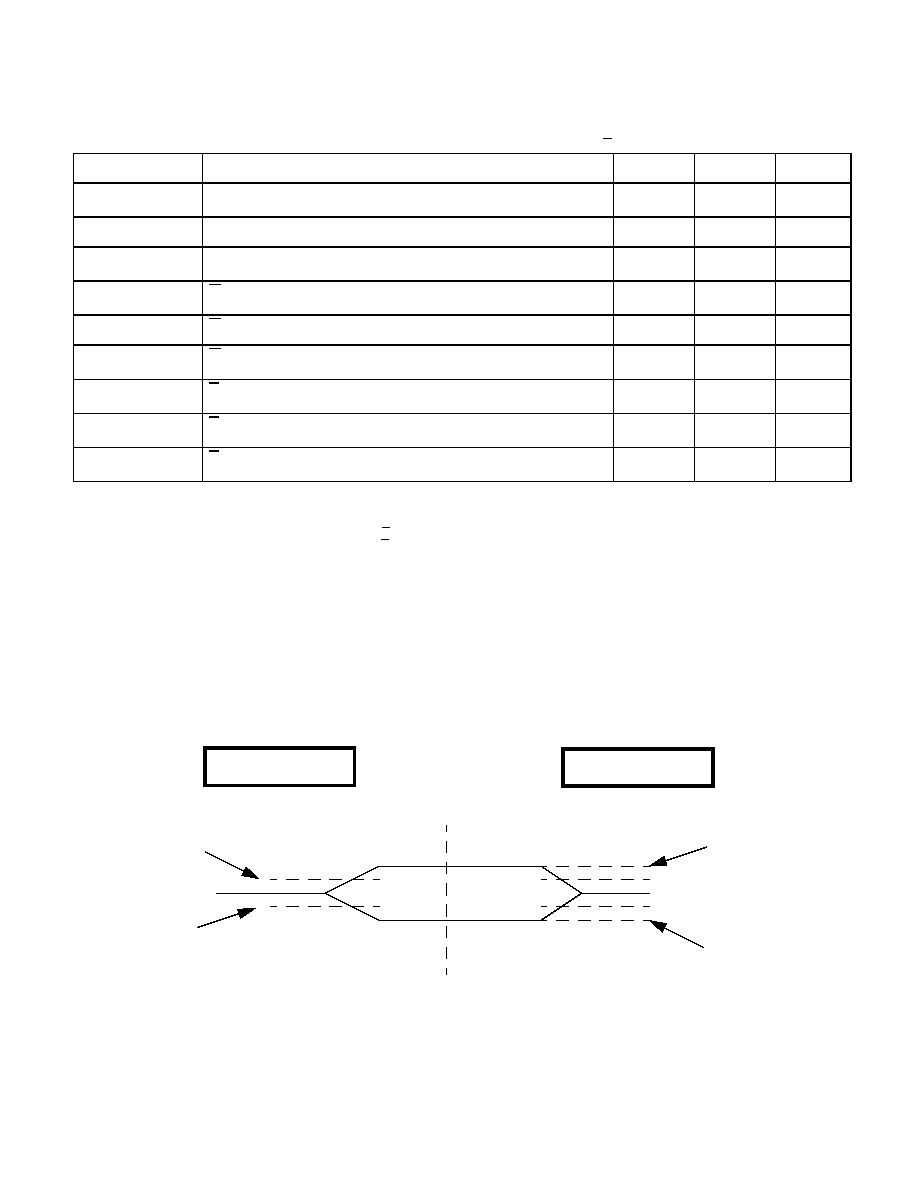

VLOAD + 500mV

VLOAD - 500mV

VLOAD

VH - 500mV

VL + 500mV

Active to High Z Levels

High Z to Active Levels

Figure 3. 5-Volt SRAM Loading

AC CHARACTERISTICS READ CYCLE (Pre/Post-Radiation)*

-55

°C to +125°C for (C) screening and -40oC to +125oC for (W) screening (V

DD = 5.0V + 10%)

Notes: * Post-radiation performance guaranteed at 25

°C per MIL-STD-883 Method 1019.

1. Functional test.

2. Three-state is defined as a 500mV change from steady-state output voltage (see Figure 3).

3. The ET (chip enable true) notation refers to the falling edge of E. SEU immunity does not affect the read parameters.

4. The EF (chip enable false) notation refers to the rising edge of E. SEU immunity does not affect the read parameters.

SYMBOL

PARAMETER

MIN

MAX

UNIT

tAVAV

1

Read cycle time

20

ns

tAVQV

Read access time

20

ns

tAXQX

Output hold time

3

ns

tGLQX

G-controlled Output Enable time

0

ns

tGLQV

G-controlled Output Enable time (Read Cycle 3)

10

ns

tGHQZ

2

G-controlled output three-state time

10

ns

tETQX

3

E-controlled Output Enable time

3

ns

tETQV

3

E-controlled access time

20

ns

tEFQZ

1,2,4

E-controlled output three-state time

10

ns

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| 5962D1022901QXC | 64M X 40 SYNCHRONOUS DRAM, 5.4 ns, CQFP128 |

| 5962F0253401VXC | 2.5 V FIXED POSITIVE REGULATOR, CDFP16 |

| L491333DIE2V | 3.3 V FIXED POSITIVE REGULATOR, UUC |

| 5962F9654403QXA | OTHER DECODER/DRIVER, CDFP16 |

| 5962F9657601QCX | AC SERIES, 4-BIT LOOK-AHEAD CARRY GENERATOR, TRUE OUTPUT, CDIP16 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| 5962D0823001QXC | 制造商:Intersil Corporation 功能描述: |

| 5962D9563201VXC | 制造商:STMicroelectronics 功能描述:RS-432LINE DRIVERQUADFLAT16, GOLD - Bulk |

| 5962D9666301VXC | 制造商:STMicroelectronics 功能描述:RS-432LINE DRIVERQUADFLAT16, GOLD - Bulk |

| 5962F0052301QXC | 制造商:Intersil Corporation 功能描述: |

| 5962F0052301VXC | 制造商:Intersil Corporation 功能描述: |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。