- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄358627 > 33984 (Motorola, Inc.) Dual Intelligent High-Current Self-Protected Silicon High-Side Switch (4.0 mз) PDF資料下載

參數(shù)資料

| 型號: | 33984 |

| 廠商: | Motorola, Inc. |

| 英文描述: | Dual Intelligent High-Current Self-Protected Silicon High-Side Switch (4.0 mз) |

| 中文描述: | 雙智能大電流的自我保護(hù)硅高邊開關(guān)(4.0mз) |

| 文件頁數(shù): | 12/28頁 |

| 文件大?。?/td> | 492K |

| 代理商: | 33984 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁當(dāng)前第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁

33984

12

MOTOROLA ANALOG INTEGRATED CIRCUIT DEVICE DATA

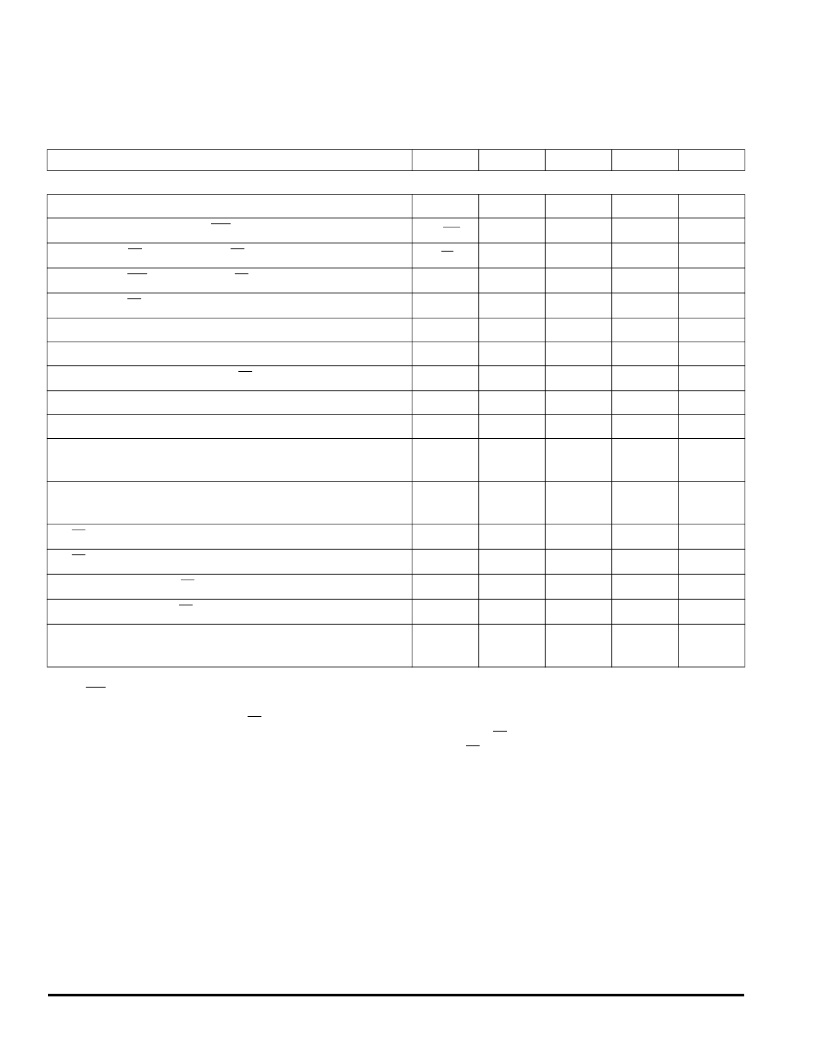

DYNAMIC ELECTRICAL CHARACTERISTICS (continued)

Characteristics noted under conditions 4.5 V

≤

V

DD

≤

5.5 V, 6.0 V

≤

V

PWR

≤

27 V, -40

°

C

≤

T

J

≤

150

°

C unless otherwise noted. Typical

values noted reflect the approximate parameter mean at T

A

= 25

°

C under nominal conditions unless otherwise noted.

Characteristic

Symbol

Min

Typ

Max

Unit

SPI INTERFACE CHARACTERISTICS

Recommended Frequency of SPI Operation

f

SPI

–

–

3.0

MHz

Required Low State Duration for

RST

(Note 24)

t

WRST

–

50

350

ns

Rising Edge of

CS

to Falling Edge of

CS

(Required Setup Time)

(Note 25)

t

CS

–

–

300

ns

Rising Edge of

RST

to Falling Edge of

CS

(Required Setup Time)

(Note 25)

t

ENBL

–

–

5.0

μ

s

Falling Edge of

CS

to Rising Edge of SCLK (Required Setup Time)

(Note 25)

t

LEAD

–

50

167

ns

Required High State Duration of SCLK (Required Setup Time)

(Note 25)

t

WSCLKh

–

–

167

ns

Required Low State Duration of SCLK (Required Setup Time)

(Note 25)

t

WSCLKl

–

–

167

ns

Falling Edge of SCLK to Rising Edge of

CS

(Required Setup Time)

(Note 25)

t

LAG

–

50

167

ns

SI to Falling Edge of SCLK (Required Setup Time)

(Note 26)

t

SI(SU)

–

25

83

ns

Falling Edge of SCLK to SI (Required Setup Time)

(Note 26)

t

SI(HOLD)

–

25

83

ns

SO Rise Time

C

L

= 200 pF

t

RSO

–

25

50

ns

SO Fall Time

C

L

= 200 pF

t

FSO

–

25

50

ns

SI,

CS

, SCLK, Incoming Signal Rise Time

(Note 26)

t

RSI

–

–

50

ns

SI,

CS

, SCLK, Incoming Signal Fall Time

(Note 26)

t

RSI

–

–

50

ns

Time from Falling Edge of

CS

to SO Low Impedance

(Note 27)

t

SO(EN)

–

–

145

ns

Time from Rising Edge of

CS

to SO High Impedance

(Note 28)

t

SO(DIS)

–

65

145

ns

Time from Rising Edge of SCLK to SO Data Valid

(Note 29)

0.2 V

DD

≤

SO

≥

0.8 V

DD

, C

L

= 200 pF

t

VALID

–

65

105

ns

Notes

24.

25.

26.

27.

28.

29.

RST

low duration measured with outputs enabled and going to OFF or disabled condition.

Maximum setup time required for the 33984 is the minimum guaranteed time needed from the microcontroller.

Rise and Fall time of incoming SI,

CS

, and SCLK signals suggested for design consideration to prevent the occurrence of double pulsing.

Time required for output status data to be available for use at SO. 1.0 k

on pullup on

CS

.

Time required for output status data to be terminated at SO. 1.0 k

on pullup on

CS

.

Time required to obtain valid data out from SO following the rise of SCLK.

F

Freescale Semiconductor, Inc.

For More Information On This Product,

Go to: www.freescale.com

n

.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| 33991 | Gauge Driver Integrated Circuit |

| 33BS | surface mount silicon Zener diodes |

| 33C408 | 4 Megabit (512K x 8-Bit) CMOS SRAM |

| 33C408RPFB-20 | 4 Megabit (512K x 8-Bit) CMOS SRAM |

| 33C408RPFB-25 | 4 Megabit (512K x 8-Bit) CMOS SRAM |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| 33984B | 制造商:FREESCALE 制造商全稱:Freescale Semiconductor, Inc 功能描述:Dual Intelligent High-Current Self Protected Silicon High-Side Switch (4.0 mohm) |

| 33984B_09 | 制造商:FREESCALE 制造商全稱:Freescale Semiconductor, Inc 功能描述:Dual Intelligent High-current Self-protected Silicon High Side Switch (4.0 mΩ) |

| 33984B_10 | 制造商:FREESCALE 制造商全稱:Freescale Semiconductor, Inc 功能描述:Dual Intelligent High-current |

| 33984C | 制造商:FREESCALE 制造商全稱:Freescale Semiconductor, Inc 功能描述:Dual Intelligent High-current Self-protected Silicon High Side Switch (4.0 mΩ) |

| 33-987-BU | 制造商:GC Electronics 功能描述: |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。