- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄373786 > ZL50115 (Zarlink Semiconductor Inc.) 32, 64 and 128 Channel CESoP Processors PDF資料下載

參數(shù)資料

| 型號(hào): | ZL50115 |

| 廠商: | Zarlink Semiconductor Inc. |

| 英文描述: | 32, 64 and 128 Channel CESoP Processors |

| 中文描述: | 32,64和128頻道CESoP處理器 |

| 文件頁(yè)數(shù): | 36/95頁(yè) |

| 文件大?。?/td> | 1157K |

| 代理商: | ZL50115 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)當(dāng)前第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)第75頁(yè)第76頁(yè)第77頁(yè)第78頁(yè)第79頁(yè)第80頁(yè)第81頁(yè)第82頁(yè)第83頁(yè)第84頁(yè)第85頁(yè)第86頁(yè)第87頁(yè)第88頁(yè)第89頁(yè)第90頁(yè)第91頁(yè)第92頁(yè)第93頁(yè)第94頁(yè)第95頁(yè)

ZL50115/16/17/18/19/20

Data Sheet

36

Zarlink Semiconductor Inc.

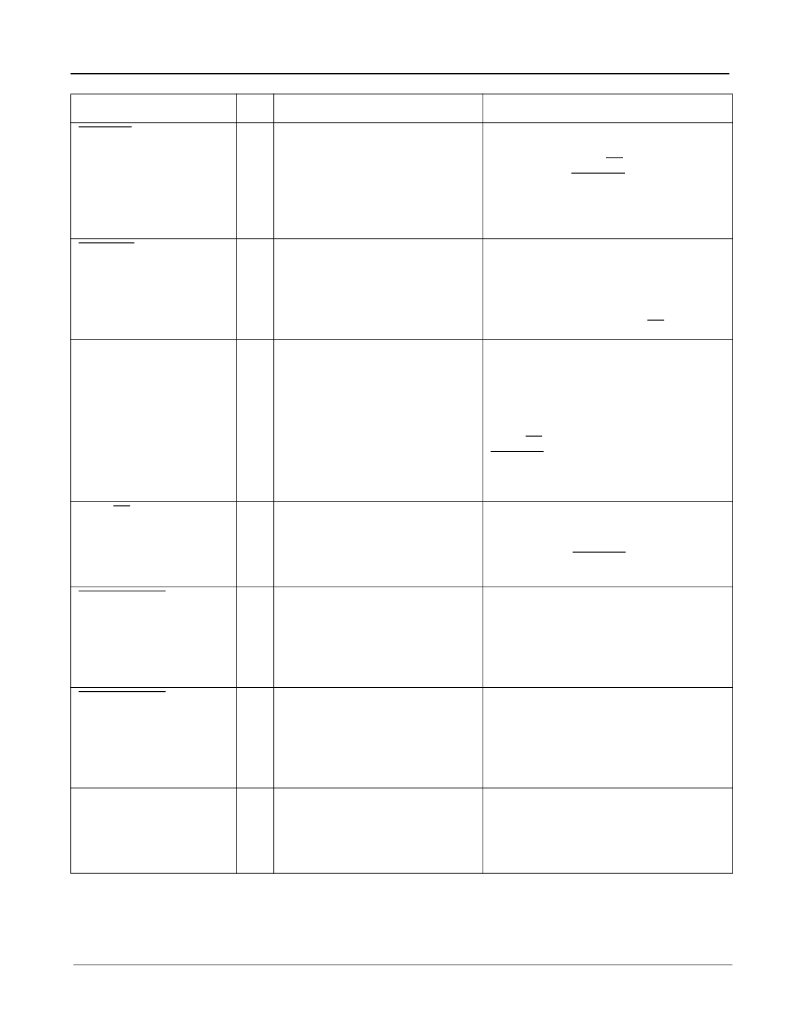

CPU_CS

I U

N21

CPU Chip Select. Synchronous to rising

edge of CPU_CLK and active low. Is

asserted with CPU_TS_ALE. Must be

asserted with CPU_OE to

asynchronously enable the CPU_DATA

output during a read, including DMA

read.

CPU_WE

I

M21

CPU Write Enable. Synchronously

asserted with respect to CPU_CLK

rising edge, and active low. Used for

CPU writes from the processor to

registers within the ZL5011x. Asserted

one clock cycle after CPU_TS_ALE.

CPU_OE

I

M22

CPU Output Enable.

Synchronously asserted with respect to

CPU_CLK rising edge, and active low.

Used for CPU reads from the processor

to registers within the ZL5011x.

Asserted one clock cycle after

CPU_TS_ALE. Must be asserted with

CPU_CS to asynchronously enable the

CPU_DATA output during a read,

including DMA read.

CPU_TS_ALE

I

M20

Synchronous input with rising edge of

CPU_CLK.

Latch Enable (ALE), active high signal.

Asserted with CPU_CS, for a single

clock cycle.

CPU_SDACK1

I

A21

CPU/DMA 1 Acknowledge Input. Active

low synchronous to CPU_CLK rising

edge. Used to acknowledge request

from ZL5011x for a DMA write

transaction. Only used for DMA

transfers, not for normal register access.

CPU_SDACK2

I

L21

CPU/DMA 2 Acknowledge Input Active

low synchronous to CPU_CLK rising

edge. Used to acknowledge request

from ZL5011x for a DMA read

transaction. Only used for DMA

transfers, not for normal register access.

CPU_CLK

I

L19

CPU PowerQUICC II Bus Interface

clock input. 66 MHz clock, with minimum

of 6 ns high/low time. Used to time all

host interface signals into and out of

ZL5011x device.

Signal

I/O

Package Balls

Description

Table 10 - CPU Interface Package Ball Definition (continued)

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| ZL50116 | 32, 64 and 128 Channel CESoP Processors |

| ZL50117 | 32, 64 and 128 Channel CESoP Processors |

| ZL50118 | 32, 64 and 128 Channel CESoP Processors |

| ZL50119 | 32, 64 and 128 Channel CESoP Processors |

| ZL50120 | 32, 64 and 128 Channel CESoP Processors |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| ZL50115GAG | 制造商:Microsemi Corporation 功能描述:SWIT FABRIC 1K X 1K 1.8V/3.3V 324BGA - Trays 制造商:Microsemi Corporation 功能描述:IC CESOP PROCESSOR 32CH 324PBGA |

| ZL50115GAG2 | 制造商:Microsemi Corporation 功能描述:PB FREE 1 TDM + 1 ETHERNET - Trays 制造商:Microsemi Corporation 功能描述:IC CESOP PROCESSOR 32CH 324PBGA |

| ZL50116 | 制造商:ZARLINK 制造商全稱:Zarlink Semiconductor Inc 功能描述:32, 64 and 128 Channel CESoP Processors |

| ZL50116GAG | 制造商:Microsemi Corporation 功能描述:2 TDM + 1 ETHERNET - Trays 制造商:MICROSEMI CONSUMER MEDICAL PRODUCT GROUP 功能描述:IC CESOP PROCESSOR 64CH 324PBGA 制造商:Microsemi Corporation 功能描述:IC CESOP PROCESSOR 64CH 324PBGA |

| ZL50116GAG2 | 制造商:Microsemi Corporation 功能描述:PB FREE 2 TDM + 1 ETHERNET - Trays 制造商:MICROSEMI CONSUMER MEDICAL PRODUCT GROUP 功能描述:IC CESOP PROCESSOR 64CH 324PBGA 制造商:Microsemi Corporation 功能描述:IC CESOP PROCESSOR 64CH 324PBGA |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。