- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄373783 > ZL30100QDC (ZARLINK SEMICONDUCTOR INC) T1/E1 System Synchronizer PDF資料下載

參數(shù)資料

| 型號: | ZL30100QDC |

| 廠商: | ZARLINK SEMICONDUCTOR INC |

| 元件分類: | 通信及網(wǎng)絡(luò) |

| 英文描述: | T1/E1 System Synchronizer |

| 中文描述: | SPECIALTY TELECOM CIRCUIT, PQFP64 |

| 封裝: | 10 X 10 MM, 1 MM HEIGHT, MS-026ACD, TQFP-64 |

| 文件頁數(shù): | 16/34頁 |

| 文件大?。?/td> | 560K |

| 代理商: | ZL30100QDC |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁當(dāng)前第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁

ZL30100

Data Sheet

16

Zarlink Semiconductor Inc.

In Normal mode, the DCO provides an output signal which is frequency and phase locked to the selected input

reference signal.

In Holdover mode, the DCO is free running at a frequency equal to the frequency that the DCO was generating in

Normal mode. The frequency in Holdover mode is calculated from frequency samples stored 26 ms to 52 ms before

the ZL30100 entered Holdover mode.

In Freerun mode, the DCO is free running with an accuracy equal to the accuracy of the OSCi 20 MHz source.

Lock Indicator

- the lock detector monitors if the output value of the phase detector is within the phase-lock-

window for a certain time. The selected phase-lock-window guarantees the stable operation of the LOCK pin with

maximum network jitter and wander on the reference input. If the DPLL is locked and then goes into Holdover mode

(auto or manual), the LOCK pin will initially stay high for 1 s. If at that point the DPLL is still in holdover mode, the

LOCK pin will go low; subsequently the LOCK pin will not return high for at least the full lock-time duration. In

Freerun mode the LOCK pin will go low immediately.

3.5 Frequency Synthesizers

The output of the DCO is used by the frequency synthesizers to generate the C1.5o, C2o, C4o, C8o, C16o, C32o

and C65o clocks and the F4o, F8o, F16o, F32o and F65o frame pulses which are synchronized to the selected

reference input (REF0 or REF1). The frequency synthesizers use digital techniques to generate output clocks and

advanced noise shaping techniques to minimize the output jitter. The clock and frame pulse outputs have limited

driving capability and should be buffered when driving high capacitance loads.

3.6 State Machine

As shown in Figure 1, the control state machine controls the TIE Corrector Circuit and the DPLL. The control of the

ZL30100 is based on the inputs MODE_SEL1:0, REF_SEL and HMS.

3.7 Master Clock

The ZL30100 can use either a clock or crystal as the master timing source. For recommended master timing

circuits, see the Applications - Master Clock section.

4.0 Control and Modes of Operation

4.1 Out of Range Selection

The frequency out of range limits for the precise frequency monitoring in the reference monitors are selected by the

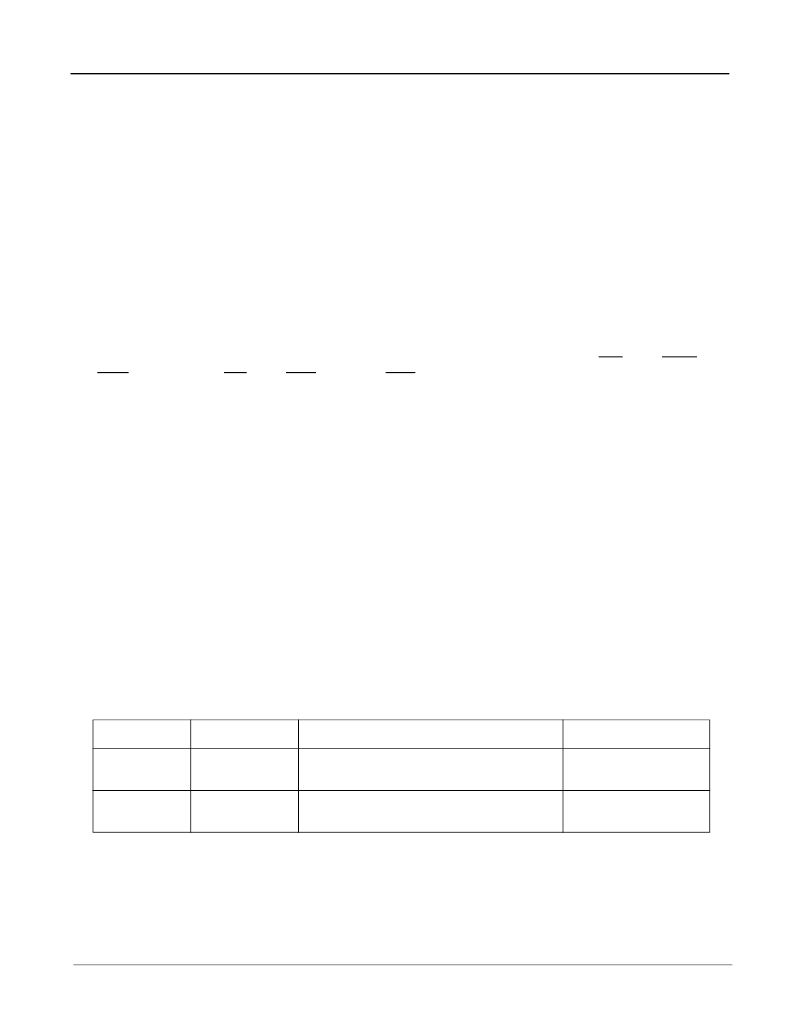

OOR_SEL pin, see Table 1.

OOR_SEL

Application

Applicable Standard

Out Of Range Limits

0

DS1

ANSI T1.403

Telcordia GR-1244-CORE Stratum 4/4E

64 - 83 ppm

1

E1

ITU-T G.703

ETSI ETS 300 011

100 - 130 ppm

Table 1 - Out of Range Limits Selection

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| ZL30101QDG1 | T1/E1 Stratum 3 System Synchronizer |

| ZL30101 | T1/E1 Stratum 3 System Synchronizer |

| ZL30101QDC | T1/E1 Stratum 3 System Synchronizer |

| ZL30102QDG1 | T1/E1 Stratum 4/4E Redundant System Clock Synchronizer for DS1/E1 and H.110 |

| ZL30102 | T1/E1 Stratum 4/4E Redundant System Clock Synchronizer for DS1/E1 and H.110 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| ZL30100QDG1 | 制造商:Microsemi Corporation 功能描述:SYS SYNCHRONIZER 64TQFP - Trays 制造商:Microsemi Corporation 功能描述:T1/E1 SYSTEM SYNCHRONIZER 制造商:MICROSEMI CONSUMER MEDICAL PRODUCT GROUP 功能描述:IC SYNCHRONIZER T1/E1 64TQFP 制造商:Microsemi Corporation 功能描述:IC SYNCHRONIZER T1/E1 64TQFP |

| ZL30101 | 制造商:ZARLINK 制造商全稱:Zarlink Semiconductor Inc 功能描述:T1/E1 Stratum 3 System Synchronizer |

| ZL30101_06 | 制造商:ZARLINK 制造商全稱:Zarlink Semiconductor Inc 功能描述:T1/E1 Stratum 3 System Synchronizer |

| ZL30101QDC | 制造商:Microsemi Corporation 功能描述: |

| ZL30101QDG1 | 制造商:Microsemi Corporation 功能描述:SYS SYNCHRONIZER 64TQFP - Trays |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。