- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄376462 > XRT79L74IB (EXAR CORP) 4 - CHANNEL DS3/E3 ATM UNI/PPP COMBO IC PDF資料下載

參數(shù)資料

| 型號: | XRT79L74IB |

| 廠商: | EXAR CORP |

| 元件分類: | 數(shù)字傳輸電路 |

| 英文描述: | 4 - CHANNEL DS3/E3 ATM UNI/PPP COMBO IC |

| 中文描述: | ATM NETWORK INTERFACE, PBGA456 |

| 封裝: | 27 X 27 MM, 1 MM PITCH, PLASTIC, BGA-456 |

| 文件頁數(shù): | 39/70頁 |

| 文件大?。?/td> | 547K |

| 代理商: | XRT79L74IB |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁當前第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁

PRELIMINARY

XRT79L74

REV. P1.0.0

4 - CHANNEL DS3/E3 ATM UNI/PPP COMBO IC

37

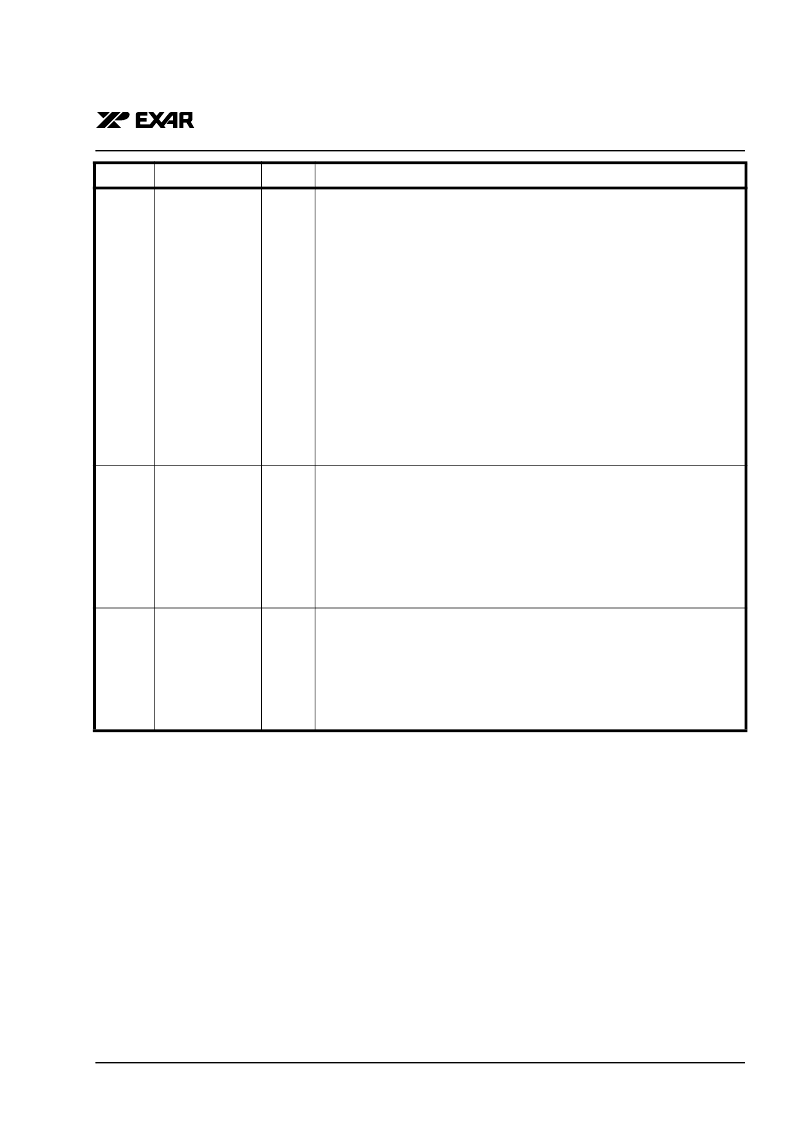

B16

RxUPrty/

RxPPrty

O

Receive UTOPIA Interface - Parity Output pin/Receive POS-PHY Interface -

Parity Output:

The function of this output pin depends upon whether the XRT79L74 has been

configured to operate in the ATM UNI or the PPP Modes.

ATM UNI Mode - RxUPrty:

The Receive UTOPIA interface block will compute the odd-parity value of each

byte (or word) that it will place in the Receive UTOPIA Data Bus. This odd-par-

ity value will be output on this pin, while the corresponding byte (or word) is

present on the Receive UTOPIA Data Bus

PPP Mode - RxPPrty:

The Receive POS-PHY Interface block will compute the odd-parity value of

each byte (or word) that it will place in the Receive POS-PHY Data Bus. This

odd parity value will be output on this pin, which the corresponding byte (or

word) is present on the Receive POS-PHY Data Bus.

N

OTE

:

This output pin will be in-active if the user has configured the XRT79L74

device to operate in either the Clear-Channel Framer or in the High-

Speed HDLC Controller Modes.

E13

RxPEOP

O

Receive POS-PHY Interface - End of Packet:

The XRT79L74 drives this output pin "High" whenever the last byte of a given

Packet is being output via the RxPData[15:0] data bus.

N

OTES

:

1.

This output pin is only valid when the XRT79L74 is configured to

operate in the PPP Mode.

2.

This output pin is only valid when the Receive POS-PHY Interface -

Read Enable Output pin.

A9

RxPDVAL

O

Receive POS-PHY Interface Signal Valid Indicator:

This output signal indicates whether or not the Receive POS-PHY Interface sig-

nals (e.g., PRData[15:0], RxPSOP, RxPEOP, RxPPrty, RxPERR) are valid.

This output pin will be driven "High", when these signals are valid. Conversely,

this output pin will be driven "Low" when these signals are NOT valid.

N

OTE

:

This output pin is only active if the XRT79L74 has been configured to

operate in the PPP Mode.

P

IN

#

N

AME

TYPE

D

ESCRIPTION

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| XRT8000ID | Clock Synchronizer/Adapter for Communications |

| XRT8000 | Clock Synchronizer/Adapter for Communications(用于通訊的時鐘同步設備/調(diào)整器) |

| XRT8001 | WAN Clock for T1 and E1 Systems |

| XRT8001ID | WAN Clock for T1 and E1 Systems |

| XRT8001IP | WAN Clock for T1 and E1 Systems |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| XRT8000 | 制造商:EXAR 制造商全稱:EXAR 功能描述:Clock Synchronizer/Adapter for Communications |

| XRT8000_06 | 制造商:EXAR 制造商全稱:EXAR 功能描述:Clock Synchronizer/Adapter for Communications |

| XRT8000D | 制造商:EXAR 制造商全稱:EXAR 功能描述:CLOCK SYNCHRONIZER/ADAPTER FOR COMMUNICATIONS |

| XRT8000ES | 功能描述:鎖相環(huán) - PLL WAN CLOCK RoHS:否 制造商:Silicon Labs 類型:PLL Clock Multiplier 電路數(shù)量:1 最大輸入頻率:710 MHz 最小輸入頻率:0.002 MHz 輸出頻率范圍:0.002 MHz to 808 MHz 電源電壓-最大:3.63 V 電源電壓-最小:1.71 V 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 封裝 / 箱體:QFN-36 封裝:Tray |

| XRT8000ID | 制造商:EXAR 制造商全稱:EXAR 功能描述:Clock Synchronizer/Adapter for Communications |

發(fā)布緊急采購,3分鐘左右您將得到回復。