- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄376462 > XRT75R12DIB (EXAR CORP) TWELVE CHANNEL E3/DS3/STS-1 LINE INTERFACE UNIT WITH SONET DESYNCHRONIZER PDF資料下載

參數(shù)資料

| 型號(hào): | XRT75R12DIB |

| 廠商: | EXAR CORP |

| 元件分類: | 數(shù)字傳輸電路 |

| 英文描述: | TWELVE CHANNEL E3/DS3/STS-1 LINE INTERFACE UNIT WITH SONET DESYNCHRONIZER |

| 中文描述: | DATACOM, PCM TRANSCEIVER, PBGA420 |

| 封裝: | 35 X 35 MM, TBGA-420 |

| 文件頁數(shù): | 122/131頁 |

| 文件大小: | 717K |

| 代理商: | XRT75R12DIB |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁第113頁第114頁第115頁第116頁第117頁第118頁第119頁第120頁第121頁當(dāng)前第122頁第123頁第124頁第125頁第126頁第127頁第128頁第129頁第130頁第131頁

XRT75R12D

REV. P1.0.1

TWELVE CHANNEL E3/DS3/STS-1 LINE INTERFACE UNIT WITH SONET DESYNCHRONIZER

PRELIMINARY

117

If the LIU has been configured to operate in the Hardware Mode.

Then the user should tie pin 43 (JATx/JARx*) to "1".

e. Enable the "SONET APS Recovery Time" Mode

Finally, if the user intends to use the LIU in an Application that is required to reacquire proper SONET and DS3

traffic, prior within 50ms of an APS (Automatic Protection Switching) event (per Telcordia GR-253-CORE), then

the user should set Bit 4 (SONET APS Recovery Time Disable), within the "Jitter Attenuator Control" Register,

to "0" as depicted below.

N

OTES

:

1.

The ability to disable the "SONET APS Recovery Time" mode is only available if the LIU is operating in the Host

Mode. If the LIU is operating in the "Hardware" Mode, then this "SONET APS Recovery Time Mode" feature will

always be enabled.

The "SONET APS Recovery Time" mode will be discussed in greater detail in “Section 8.8.3, How does the LIU

permit the user to comply with the SONET APS Recovery Time requirements of 50ms (per Telcordia GR-253-

CORE)” on page 121.

Recommendations on Pre-Processing the Gapped Clocks (from the Mapper/ASIC Device)

prior to routing this DS3 Clock and Data-Signals to the Transmit Inputs of the LIU

In order to minimize the effects of "Clock-Gapping" Jitter within the DS3 signal that is ultimately transmitted to

the DS3 Line (or facility), we recommend that some "pre-processing" of the "Data-Signals" and "Clock-Signals"

(which are output from the Mapper device) be implemented prior to routing these signals to the "Transmit

Inputs" of the LIU.

8.8.2.1

SOME NOTES PRIOR TO STARTING THIS DISCUSSION:

2.

8.8.2

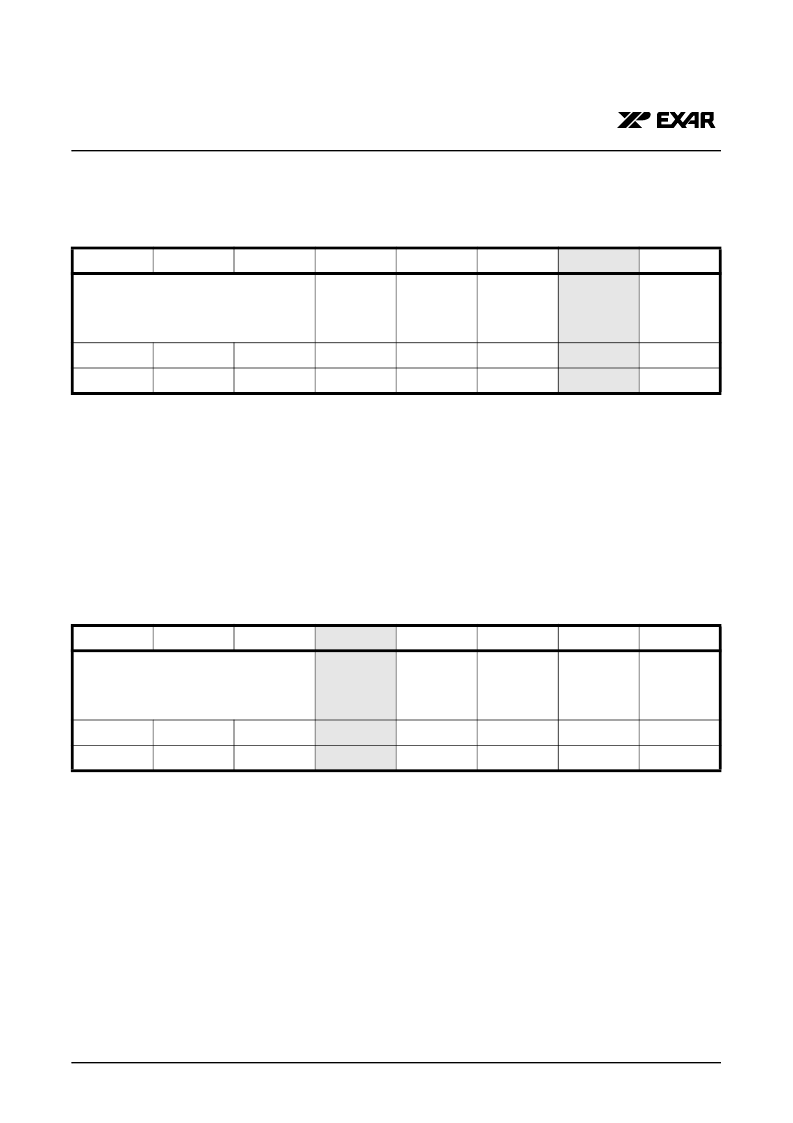

JITTER ATTENUATOR CONTROL REGISTER - CHANNEL 0 ADDRESS LOCATION = 0X07

CHANNEL 1 ADDRESS LOCATION = 0X0F

CHANNEL 2 ADDRESS LOCATION = 0X17

B

IT

7

B

IT

6

B

IT

5

B

IT

4

B

IT

3

B

IT

2

B

IT

1

B

IT

0

Unused

SONET APS

Recovery

Time

DisableCh_n

JA RESET

Ch_n

JA1 Ch_n

JA in Tx Path

Ch_n

JA0 Ch_n

R/O

R/O

R/O

R/W

R/W

R/W

R/W

R/W

0

0

0

0

0

0

1

1

JITTER ATTENUATOR CONTROL REGISTER - CHANNEL 0 ADDRESS LOCATION = 0X07

CHANNEL 1 ADDRESS LOCATION = 0X0F

CHANNEL 2 ADDRESS LOCATION = 0X17

B

IT

7

B

IT

6

B

IT

5

B

IT

4

B

IT

3

B

IT

2

B

IT

1

B

IT

0

Unused

SONET APS

Recovery

Time

DisableCh_n

JA RESET

Ch_n

JA1 Ch_n

JA in Tx Path

Ch_n

JA0 Ch_n

R/O

R/O

R/O

R/W

R/W

R/W

R/W

R/W

0

0

0

0

0

0

0

1

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| XRT75R12 | TWELVE CHANNEL E3/DS3/STS-1 LINE INTERFACE UNIT WITH JITTER ATTENUATOR |

| XRT75R12IB | TWELVE CHANNEL E3/DS3/STS-1 LINE INTERFACE UNIT WITH JITTER ATTENUATOR |

| XRT75VL00 | E3/DS3/STS-1 LINE INTERFACE UNIT WITH JITTER ATTENUATOR |

| XRT75VL00IV | E3/DS3/STS-1 LINE INTERFACE UNIT WITH JITTER ATTENUATOR |

| XRT79L71 | 1 - CHANNEL DS3/E3 ATM UNI/PPP COMBO IC |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| XRT75R12DIB-F | 功能描述:網(wǎng)絡(luò)控制器與處理器 IC 12 Channel 3.3V-5V temp -45 to 85C RoHS:否 制造商:Micrel 產(chǎn)品:Controller Area Network (CAN) 收發(fā)器數(shù)量: 數(shù)據(jù)速率: 電源電流(最大值):595 mA 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:PBGA-400 封裝:Tray |

| XRT75R12DIB-L | 功能描述:LIN 收發(fā)器 Synch RoHS:否 制造商:NXP Semiconductors 工作電源電壓: 電源電流: 最大工作溫度: 封裝 / 箱體:SO-8 |

| XRT75R12ES | 功能描述:時(shí)鐘合成器/抖動(dòng)清除器 12CH T3/E3/STS1LIUJA 3.3V W/REDUNDANCY RoHS:否 制造商:Skyworks Solutions, Inc. 輸出端數(shù)量: 輸出電平: 最大輸出頻率: 輸入電平: 最大輸入頻率:6.1 GHz 電源電壓-最大:3.3 V 電源電壓-最小:2.7 V 封裝 / 箱體:TSSOP-28 封裝:Reel |

| XRT75R12IB | 功能描述:外圍驅(qū)動(dòng)器與原件 - PCI 12CH E3/DS3/STS W/JITTER R3 TECH RoHS:否 制造商:PLX Technology 工作電源電壓: 最大工作溫度: 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:FCBGA-1156 封裝:Tray |

| XRT75R12IB-F | 功能描述:外圍驅(qū)動(dòng)器與原件 - PCI 12 Channel 3.3V-5V temp -45 to 85C RoHS:否 制造商:PLX Technology 工作電源電壓: 最大工作溫度: 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:FCBGA-1156 封裝:Tray |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。