- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄376461 > XRT7295AT (Exar Corporation) DS3/Sonet STS-1 Integrated Line Receiver PDF資料下載

參數(shù)資料

| 型號: | XRT7295AT |

| 廠商: | Exar Corporation |

| 英文描述: | DS3/Sonet STS-1 Integrated Line Receiver |

| 中文描述: | DS3/Sonet STS - 1的集成線路接收器 |

| 文件頁數(shù): | 14/18頁 |

| 文件大小: | 1072K |

| 代理商: | XRT7295AT |

XRT7295AT

14

Rev.1.20

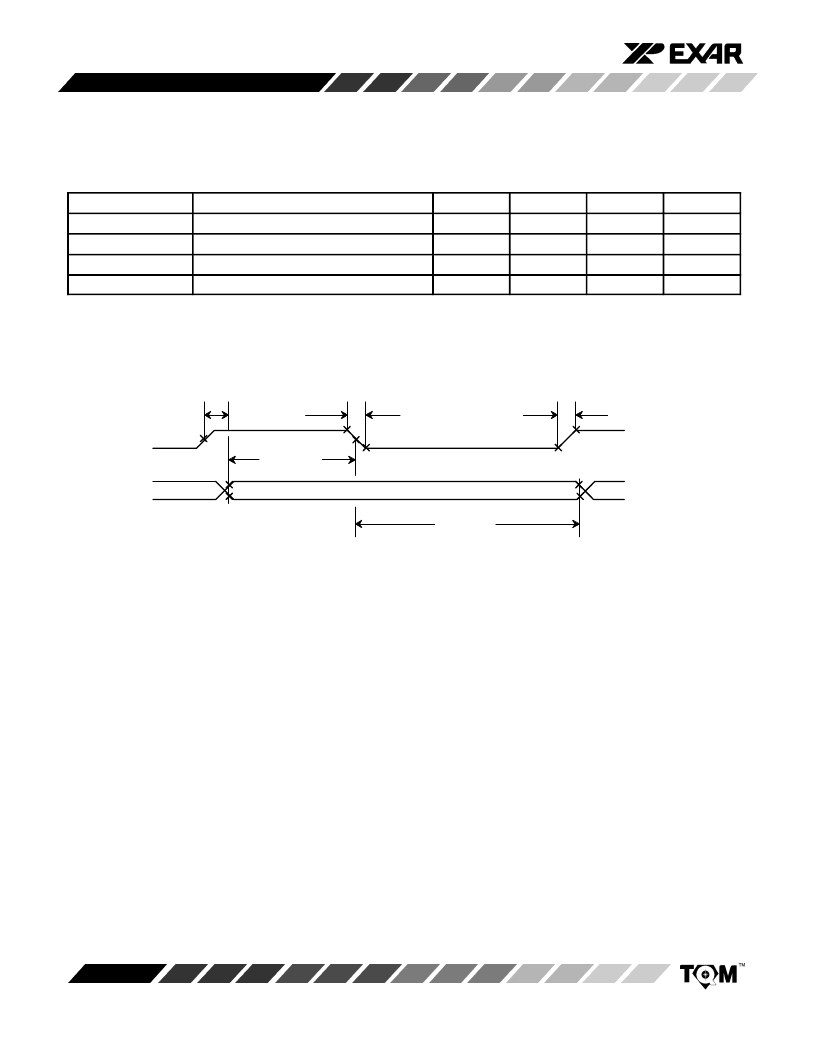

TIMING CHARACTERISTICS

Test Conditions: All Timing Characteristics are Measrured with 10pF Loading, -40

°

C

±

T

A

±

+85

°

C, V

DD

=

5V

±

10%

Symbol

tRCH1RCH2

Parameter

Clock Rise Time (10% - 90%)

Min

Typ

Max

4

Unit

ns

tRCL2RCL1

tRCHRDV

Clock Fall Time (10% - 90%)

Receive Propagation Delay

1

4

ns

ns

0.6

3.7

Clock Duty Cycle

45

50

55

%

Table 7. System Interface Timing Characteristics

Figure 11. Timing Diagram for System Interface

RCLK

(RC)

RPDATA

OR

RNDATA

(RD)

tRCHRDV

tRCL2RCL1

tRCH1RCH2

tRCLRDX

tRDVRCL

BOARD LAYOUT CONSIDERATIONS

Power Supply Bypassing

Figure 12

illustrates the recommended power supply

bypassing network. A 0.1

μ

F capacitor bypasses the

digital supplies. The analog supply V

DD

A is bypassed by

using a 0.1

μ

F capacitor and a shield bead that removes

significantamountsofhigh-frequencynoisegeneratedby

the system and by the device logic.

high-frequency (low lead inductance) capacitors should

be used.

Finally, it is most important that all ground

connections be made to a low-impedance ground plane.

Good quality,

Receive Input

The connections to the receive input pin, R

IN

, must be

carefully considered. Noise-coupling must be minimized

along the path from the signal entering the board to the

input pin. Any noise coupled into the XRT7295AT input

directly degrades the signal-to-noise ratio of the input

signal and may degrade sensitivity.

PLL Filter Capacitor

The PLL filter capacitor between pins LPF1 and LPF2

mustbeplacedasclosetothechipaspossible. TheLPF1

and LPF2 pins are adjacent, allowing for short lead

lengths with no crossovers to the external capacitor.

Noise-coupling into the LPF1 and LPF2 pins may

degrade PLL performance.

Handling Precautions

Although protection circuitry has been designed into this

device, proper precautions should be taken to avoid

exposure

to

electrostatic

handling and mounting.

discharge

(ESD)

during

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| XRT7295ATIW | DS3/Sonet STS-1 Integrated Line Receiver |

| XRT7295 | () |

| XRT7296 | INTEGRATED LINE TRANSMITTER |

| XRT7296IP | INTEGRATED LINE TRANSMITTER |

| XRT7296IW | INTEGRATED LINE TRANSMITTER |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| XRT7295AT_10 | 制造商:EXAR 制造商全稱:EXAR 功能描述:DS3 SONET STS1 Integrated Line Receiver |

| XRT7295ATIW | 功能描述:外圍驅(qū)動器與原件 - PCI RoHS:否 制造商:PLX Technology 工作電源電壓: 最大工作溫度: 安裝風格:SMD/SMT 封裝 / 箱體:FCBGA-1156 封裝:Tray |

| XRT7295ATIW-F | 功能描述:外圍驅(qū)動器與原件 - PCI -.5V--6.5V temp -45 to 85C RoHS:否 制造商:PLX Technology 工作電源電壓: 最大工作溫度: 安裝風格:SMD/SMT 封裝 / 箱體:FCBGA-1156 封裝:Tray |

| XRT7295ATIW-F | 制造商:Exar Corporation 功能描述:T3/E3 LIU IC |

| XRT7295ATIWTR | 功能描述:外圍驅(qū)動器與原件 - PCI RoHS:否 制造商:PLX Technology 工作電源電壓: 最大工作溫度: 安裝風格:SMD/SMT 封裝 / 箱體:FCBGA-1156 封裝:Tray |

發(fā)布緊急采購,3分鐘左右您將得到回復。