- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄16492 > XR16V554IV80-0A-EB (Exar Corporation)EVAL BOARD FOR XR16V554 80LQFP PDF資料下載

參數(shù)資料

| 型號: | XR16V554IV80-0A-EB |

| 廠商: | Exar Corporation |

| 文件頁數(shù): | 23/43頁 |

| 文件大小: | 0K |

| 描述: | EVAL BOARD FOR XR16V554 80LQFP |

| 標準包裝: | 1 |

| 系列: | * |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁當前第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁

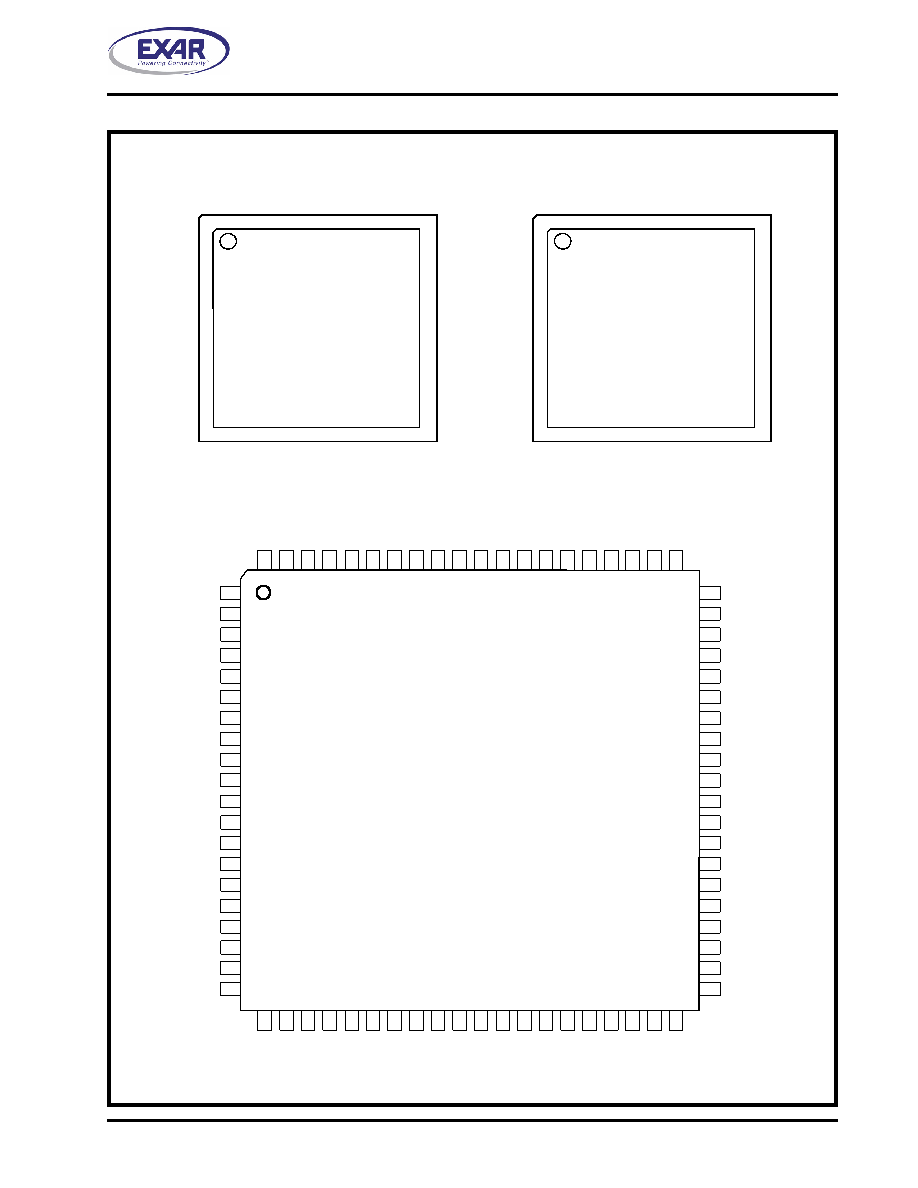

FIGURE 3. PIN OUT ASSIGNMENT FOR 48-PIN QFN PACKAGE AND 80-PIN LQFP PACKAGE

48

47

46

45

44

43

42

41

40

39

38

37

1

2

3

4

5

6

7

8

9

10

11

12

36

35

34

33

32

31

30

29

28

27

26

25

13

14

15

16

17

18

19

20

21

22

23

24

CTSA#

VCC

RTSA#

INTA

CSA#

TXA

IOW#

TXB

INTB

CSB#

RTSB#

CTSB#

RXB

16/

68#

A2

A1

A0

XTAL1

XTAL2

R

ESET

GN

D

RXC

CT

SC#

VCC

RXD

CTSD#

GND

RTSD#

INTD

CSD#

TXD

IOR#

TXC

CSC#

INTC

RTSC#

RXA

GN

D

D7

D6

D5

D4

D3

D2

D1

D0

IN

TSEL

VC

C

XR16V554

48-pin QFN

Intel Mode

(16/68# pin connected to VCC)

48

47

46

45

44

43

42

41

40

39

38

37

1

2

3

4

5

6

7

8

9

10

11

12

36

35

34

33

32

31

30

29

28

27

26

25

13

14

15

16

17

18

19

20

21

22

23

24

CTSA#

VCC

RTSA#

INTA

CSA#

TXA

IOW#

TXB

INTB

CSB#

RTSB#

CTSB#

RXB

16/

68#

A2

A1

A0

XTAL1

XTAL2

R

ESET

GN

D

RXC

CT

SC#

VCC

RXD

CTSD#

GND

RTSD#

INTD

CSD#

TXD

IOR#

TXC

CSC#

INTC

RTSC#

RXA

GN

D

D7

D6

D5

D4

D3

D2

D1

D0

IN

TSEL

VC

C

XR16V554

48-pin QFN

Motorola Mode

(16/68# pin connected to GND)

80

79

78

77

76

75

74

73

72

71

70

69

68

67

66

65

64

63

62

61

1

2

3

4

5

6

7

8

9

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

NC

GND

NC

INTSEL

VC

C

IN

TA

TX

A

NC

TX

B

IN

TB

GN

D

NC

CDB#

RIB#

RXB

VCC

A2

A1

A0

NC

XTAL1

XTAL2

NC

RESET

RXRDY#

TXRDY#

GND

RXC

RIC#

CDC#

NC

VC

C

INT

C

TX

C

NC

TX

D

IN

TD

Intel Mode Only

60

59

58

57

56

55

54

53

52

51

50

49

48

47

46

45

44

43

42

41

10

11

12

13

14

15

16

17

18

19

20

CDD#

RID#

RXD

VCC

NC

CDA#

RIA#

RXA

GND

D0

D1

D2

NC

D3

D4

D5

D6

D7

XR16 V 554

80- pin LQFP

DS

R

A

#

CT

SA

#

DT

RA

#

RT

S

A

#

CS

A

#

IO

W

#

CSB

#

RT

S

B

#

DT

R

B

#

CT

S

B

#

DS

R

B

#

DS

RD

#

CT

S

D

#

DT

RD

#

RT

S

D

#

CS

D

#

IOR

#

CS

C

#

RT

S

C

#

DT

R

C

#

CT

S

C

#

DS

R

C

#

NC

XR16V554/554D

3

REV. 1.0.3

2.25V TO 3.6V QUAD UART WITH 16-BYTE FIFO

相關PDF資料 |

PDF描述 |

|---|---|

| 1-6374614-0 | C/A 2.0MM 62.5/125 LC-SC 10M |

| GBC22DRTN-S734 | CONN EDGECARD 44POS DIP .100 SLD |

| UPM1J820MPD6TD | CAP ALUM 82UF 63V 20% RADIAL |

| RPP30-2424SW-1 | CONV DC/DC 30W 9-36VIN 24VOUT |

| XR16V554IV-0A-EVB | EVAL BOARD FOR XR16V554 64LQFP |

相關代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| XR16V554IV80-F | 功能描述:UART 接口集成電路 2.25V-3.6V 16B FIFO temp -45 to 85C;UART RoHS:否 制造商:Texas Instruments 通道數(shù)量:2 數(shù)據(jù)速率:3 Mbps 電源電壓-最大:3.6 V 電源電壓-最小:2.7 V 電源電流:20 mA 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 封裝 / 箱體:LQFP-48 封裝:Reel |

| XR16V554IV80TR-F | 功能描述:UART 接口集成電路 XR16V554IV80TR-F RoHS:否 制造商:Texas Instruments 通道數(shù)量:2 數(shù)據(jù)速率:3 Mbps 電源電壓-最大:3.6 V 電源電壓-最小:2.7 V 電源電流:20 mA 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 封裝 / 箱體:LQFP-48 封裝:Reel |

| XR16V554IV-F | 功能描述:通用總線函數(shù) UART RoHS:否 制造商:Texas Instruments 邏輯類型:CMOS 邏輯系列:74VMEH 電路數(shù)量:1 開啟電阻(最大值): 傳播延遲時間:10.1 ns 電源電壓-最大:3.45 V 電源電壓-最小:3.15 V 最大工作溫度:+ 85 C 最小工作溫度:0 C 封裝 / 箱體:TSSOP-48 封裝:Reel |

| XR16V554IVTR-F | 功能描述:UART 接口集成電路 UART RoHS:否 制造商:Texas Instruments 通道數(shù)量:2 數(shù)據(jù)速率:3 Mbps 電源電壓-最大:3.6 V 電源電壓-最小:2.7 V 電源電流:20 mA 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 封裝 / 箱體:LQFP-48 封裝:Reel |

| XR16V564 | 制造商:EXAR 制造商全稱:EXAR 功能描述:2.25V TO 3.6V QUAD UART WITH 32-BYTE FIFO |

發(fā)布緊急采購,3分鐘左右您將得到回復。