- 您現在的位置:買賣IC網 > PDF目錄16523 > XR16V2752IL-0B-EB (Exar Corporation)EVAL BOARD FOR V2752 32QFN PDF資料下載

參數資料

| 型號: | XR16V2752IL-0B-EB |

| 廠商: | Exar Corporation |

| 文件頁數: | 36/51頁 |

| 文件大?。?/td> | 0K |

| 描述: | EVAL BOARD FOR V2752 32QFN |

| 標準包裝: | 1 |

| 系列: | * |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁當前第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁

XR16V2752

41

REV. 1.0.2

HIGH PERFORMANCE DUART WITH 64-BYTE FIFO

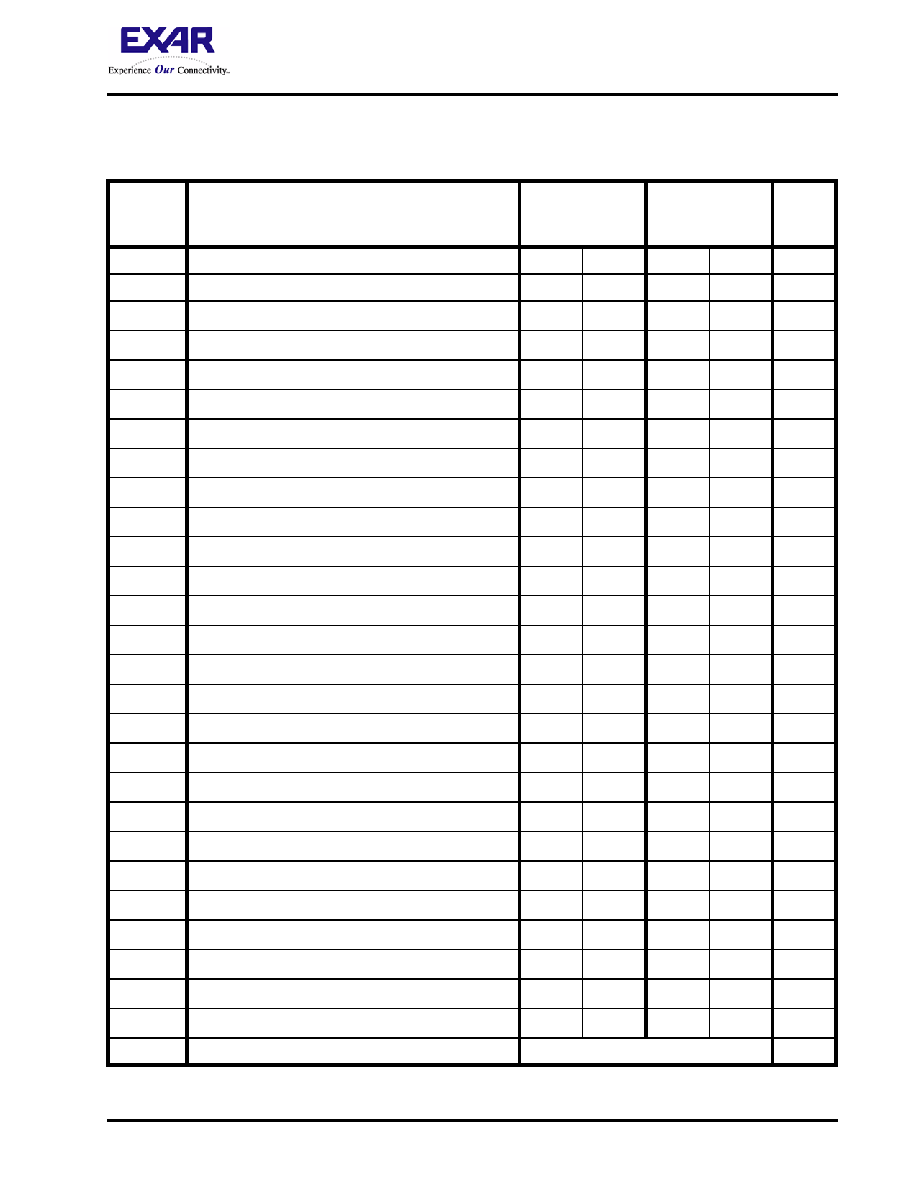

AC ELECTRICAL CHARACTERISTICS

UNLESS OTHERWISE NOTED: TA=-40

O TO +85OC, VCC=2.25 - 3.63V, 70 PF LOAD WHERE APPLICABLE

SYMBOL

PARAMETER

LIMITS

2.5V ± 10%

MIN

MAX

LIMITS

3.3V ± 10%

MIN

MAX

UNIT

XTAL1

UART Crystal Oscillator

24

MHz

ECLK

External Clock

50

64

MHz

TECLK

External Clock Time Period

10

7

ns

TAS

Address Setup Time

0

ns

TAH

Address Hold Time

0

ns

TCS

Chip Select Width

50

40

ns

TRD

IOR# Strobe Width

50

40

ns

TDY

Read Cycle Delay

50

40

ns

TRDV

Data Access Time

45

35

ns

TDD

Data Disable Time

25

ns

TWR

IOW# Strobe Width

50

40

ns

TDY

Write Cycle Delay

50

40

ns

TDS

Data Setup Time

10

ns

TDH

Data Hold Time

5

ns

TWDO

Delay From IOW# To Output

50

ns

TMOD

Delay To Set Interrupt From MODEM Input

50

ns

TRSI

Delay To Reset Interrupt From IOR#

50

ns

TSSI

Delay From Stop To Set Interrupt

1

Bclk

TRRI

Delay From IOR# To Reset Interrupt

45

ns

TSI

Delay From Stop To Interrupt

45

ns

TINT

Delay From Initial INT Reset To Transmit Start

8

24

8

24

Bclk

TWRI

Delay From IOW# To Reset Interrupt

45

ns

TSSR

Delay From Stop To Set RXRDY#

1

Bclk

TRR

Delay From IOR# To Reset RXRDY#

45

ns

TWT

Delay From IOW# To Set TXRDY#

45

ns

TSRT

Delay From Center of Start To Reset TXRDY#

8

Bclk

TRST

Reset Pulse Width

40

ns

Bclk

Baud Clock

16X or 8X of data rate

Hz

相關PDF資料 |

PDF描述 |

|---|---|

| EEU-FR1J271L | CAP ALUM 270UF 63V 20% RADIAL |

| UPA0J561MPD1TD | CAP ALUM 560UF 6.3V 20% RADIAL |

| H3AKH-3036G | IDC CABLE - HSC30H/AE30G/HPK30H |

| EBM28DTAD-S189 | CONN EDGECARD 56POS R/A .156 SLD |

| MCP1318T-46LE/OT | IC SUPERVISOR 4.6V PP/PP SOT23-5 |

相關代理商/技術參數 |

參數描述 |

|---|---|

| XR16V2752IL32 | 制造商:EXAR 制造商全稱:EXAR 功能描述:HIGH PERFORMANCE DUART WITH 64-BYTE FIFO |

| XR16V2752IL-F | 功能描述:UART 接口集成電路 UART RoHS:否 制造商:Texas Instruments 通道數量:2 數據速率:3 Mbps 電源電壓-最大:3.6 V 電源電壓-最小:2.7 V 電源電流:20 mA 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 封裝 / 箱體:LQFP-48 封裝:Reel |

| XR16V2752ILTR-F | 制造商:Exar Corporation 功能描述:UART 2-CH 64Byte FIFO 2.5V/3.3V 32-Pin QFN EP T/R 制造商:Exar Corporation 功能描述:XR16V2752ILTR-F |

| XR16V554 | 制造商:EXAR 制造商全稱:EXAR 功能描述:2.25V TO 3.6V QUAD UART WITH 16-BYTE FIFO |

| XR16V554_07 | 制造商:EXAR 制造商全稱:EXAR 功能描述:2.25V TO 3.6V QUAD UART WITH 16-BYTE FIFO |

發(fā)布緊急采購,3分鐘左右您將得到回復。