- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄4058 > XCS20XL-5PQ208C (Xilinx Inc)IC FPGA 3.3V C-TEMP HP 208PQFP PDF資料下載

參數(shù)資料

| 型號: | XCS20XL-5PQ208C |

| 廠商: | Xilinx Inc |

| 文件頁數(shù): | 27/83頁 |

| 文件大小: | 0K |

| 描述: | IC FPGA 3.3V C-TEMP HP 208PQFP |

| 產(chǎn)品變化通告: | Product Discontinuation 26/Oct/2011 |

| 標(biāo)準(zhǔn)包裝: | 24 |

| 系列: | Spartan®-XL |

| LAB/CLB數(shù): | 400 |

| 邏輯元件/單元數(shù): | 950 |

| RAM 位總計: | 12800 |

| 輸入/輸出數(shù): | 160 |

| 門數(shù): | 20000 |

| 電源電壓: | 3 V ~ 3.6 V |

| 安裝類型: | 表面貼裝 |

| 工作溫度: | 0°C ~ 85°C |

| 封裝/外殼: | 208-BFQFP |

| 供應(yīng)商設(shè)備封裝: | 208-PQFP(28x28) |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁當(dāng)前第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁

Spartan and Spartan-XL FPGA Families Data Sheet

DS060 (v2.0) March 1, 2013

33

Product Specification

R

Product Obsolete/Under Obsolescence

During Readback, 11 bits of the 16-bit checksum are added

to the end of the Readback data stream. The checksum is

computed using the CRC-16 CCITT polynomial, as shown

in Figure 29. The checksum consists of the 11 most signifi-

cant bits of the 16-bit code. A change in the checksum indi-

cates a change in the Readback bitstream. A comparison to

a previous checksum is meaningful only if the readback

data is independent of the current device state. CLB outputs

should not be included (Readback Capture option not

used), and if RAM is present, the RAM content must be

unchanged.

Statistically, one error out of 2048 might go undetected.

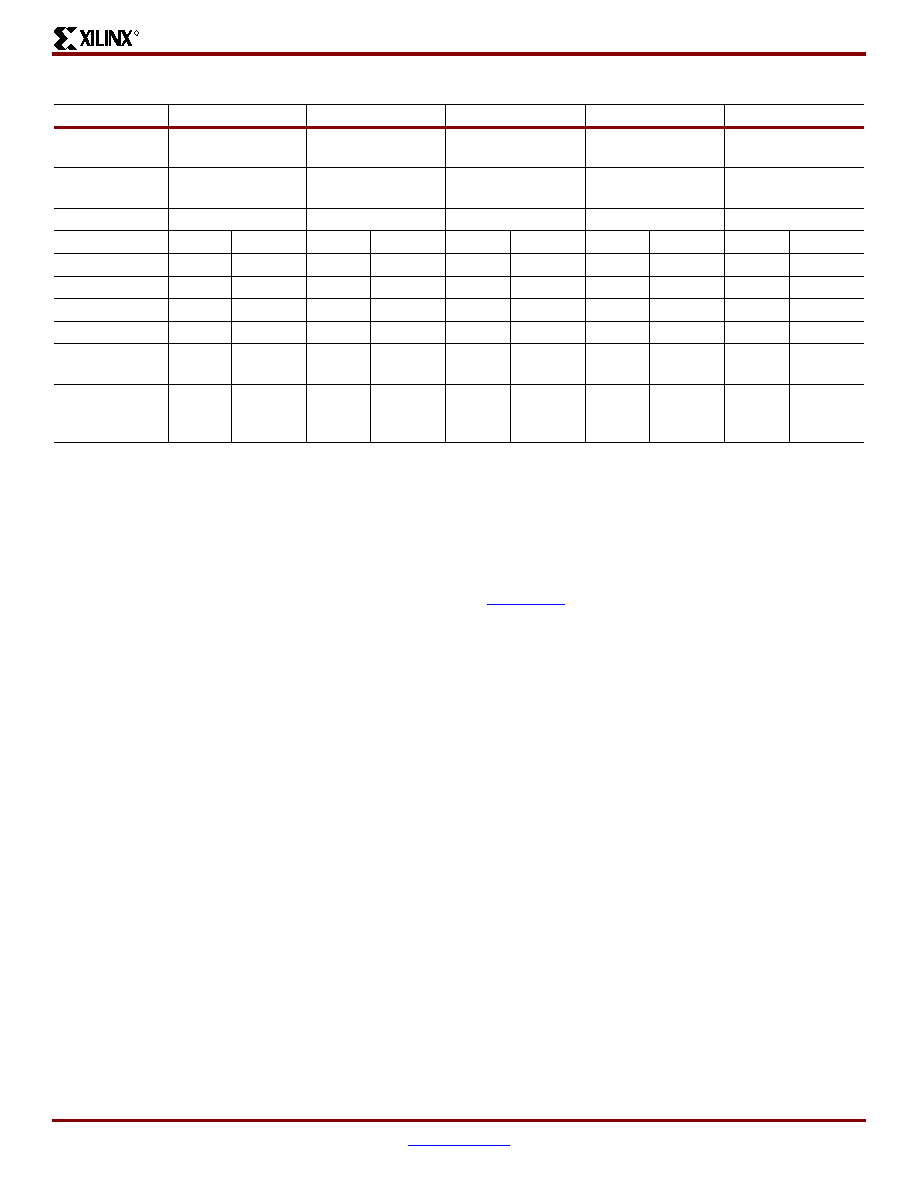

Table 17: Spartan/XL Program Data

Device

XCS05

XCS10

XCS20

XCS30

XCS40

Max System

Gates

5,000

10,000

20,000

30,000

40,000

CLBs

(Row x Col.)

100

(10 x 10)

196

(14 x 14)

400

(20 x 20)

576

(24 x 24)

784

(28 x 28)

IOBs

80

112

160

192

205(4)

Part Number

XCS05 XCS05XL XCS10 XCS10XL XCS20 XCS20XL XCS30 XCS30XL XCS40 XCS40XL

Supply Voltage

5V

3.3V5V

3.3V5V3.3V

5V3.3V5V3.3V

Bits per Frame

126

127

166

167

226

227

266

267

306

307

Frames

428

429

572

573

788

789

932

933

1,076

1,077

Program Data

53,936

54,491

94,960

95,699

178,096

179,111

247,920

249,119

329,264

330,647

PROM Size

(bits)

53,984

54,544

95,008

95,752

178,144

179,160

247,968

249,168

329,312

330,696

Express Mode

PROM Size

(bits)

-

79,072

-

128,488

-

221,056

-

298,696

-

387,856

Notes:

1.

Bits per Frame = (10 x number of rows) + 7 for the top + 13 for the bottom + 1 + 1 start bit + 4 error check bits (+1 for Spartan-XL

device)

Number of Frames = (36 x number of columns) + 26 for the left edge + 41 for the right edge + 1 (+ 1 for Spartan-XL device)

Program Data = (Bits per Frame x Number of Frames) + 8 postamble bits

PROM Size = Program Data + 40 (header) + 8, rounded up to the nearest byte

2.

The user can add more "1" bits as leading dummy bits in the header, or, if CRC = off, as trailing dummy bits at the end of any frame,

following the four error check bits. However, the Length Count value must be adjusted for all such extra "one" bits, even for extra

leading ones at the beginning of the header.

3.

Express mode adds 57 (XCS05XL, XCS10XL), or 53 (XCS20XL, XCS30XL, XCS40XL) bits per frame, + additional start-up bits.

4.

XCS40XL provided 224 max I/O in CS280 package discontinued by PDN2004-01.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| 65801-061LF | CLINCHER RECEPTACLE ASSY GOLD |

| MPC862TCZQ66B | IC MPU PWRQUICC 66MHZ 357-PBGA |

| ABB92DHBT-S329 | CONN EDGECARD 184POS R/A .050 SL |

| MPC860PCZQ50D4 | IC MPU POWERQUICC 50MHZ 357PBGA |

| MPC8360ECZUAGDGA | IC MPU POWERQUICC II PRO 740TBGA |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| XCS20XL-5PQ208I | 制造商:XILINX 制造商全稱:XILINX 功能描述:Spartan and Spartan-XL Families Field Programmable Gate Arrays |

| XCS20XL-5PQ240C | 制造商:XILINX 制造商全稱:XILINX 功能描述:Spartan and Spartan-XL Families Field Programmable Gate Arrays |

| XCS20XL-5PQ240I | 制造商:XILINX 制造商全稱:XILINX 功能描述:Spartan and Spartan-XL FPGA |

| XCS20XL-5PQ256C | 制造商:XILINX 制造商全稱:XILINX 功能描述:Spartan and Spartan-XL Families Field Programmable Gate Arrays |

| XCS20XL-5PQ256I | 制造商:XILINX 制造商全稱:XILINX 功能描述:Spartan and Spartan-XL Families Field Programmable Gate Arrays |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。