- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄4283 > XC2S200E-6PQG208C (Xilinx Inc)IC SPARTAN-IIE FPGA 200K 208PQFP PDF資料下載

參數(shù)資料

| 型號(hào): | XC2S200E-6PQG208C |

| 廠商: | Xilinx Inc |

| 文件頁(yè)數(shù): | 35/108頁(yè) |

| 文件大小: | 0K |

| 描述: | IC SPARTAN-IIE FPGA 200K 208PQFP |

| 標(biāo)準(zhǔn)包裝: | 24 |

| 系列: | Spartan®-IIE |

| LAB/CLB數(shù): | 1176 |

| 邏輯元件/單元數(shù): | 5292 |

| RAM 位總計(jì): | 57344 |

| 輸入/輸出數(shù): | 146 |

| 門(mén)數(shù): | 200000 |

| 電源電壓: | 1.71 V ~ 1.89 V |

| 安裝類型: | 表面貼裝 |

| 工作溫度: | 0°C ~ 85°C |

| 封裝/外殼: | 208-BFQFP |

| 供應(yīng)商設(shè)備封裝: | 208-PQFP(28x28) |

| 其它名稱: | 122-1324 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)當(dāng)前第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)第75頁(yè)第76頁(yè)第77頁(yè)第78頁(yè)第79頁(yè)第80頁(yè)第81頁(yè)第82頁(yè)第83頁(yè)第84頁(yè)第85頁(yè)第86頁(yè)第87頁(yè)第88頁(yè)第89頁(yè)第90頁(yè)第91頁(yè)第92頁(yè)第93頁(yè)第94頁(yè)第95頁(yè)第96頁(yè)第97頁(yè)第98頁(yè)第99頁(yè)第100頁(yè)第101頁(yè)第102頁(yè)第103頁(yè)第104頁(yè)第105頁(yè)第106頁(yè)第107頁(yè)第108頁(yè)

32

DS077-3 (v3.0) August 9, 2013

Product Specification

Spartan-IIE FPGA Family: DC and Switching Characteristics

R

— OBSOLETE — OBSOLETE — OBSOLETE — OBSOLETE —

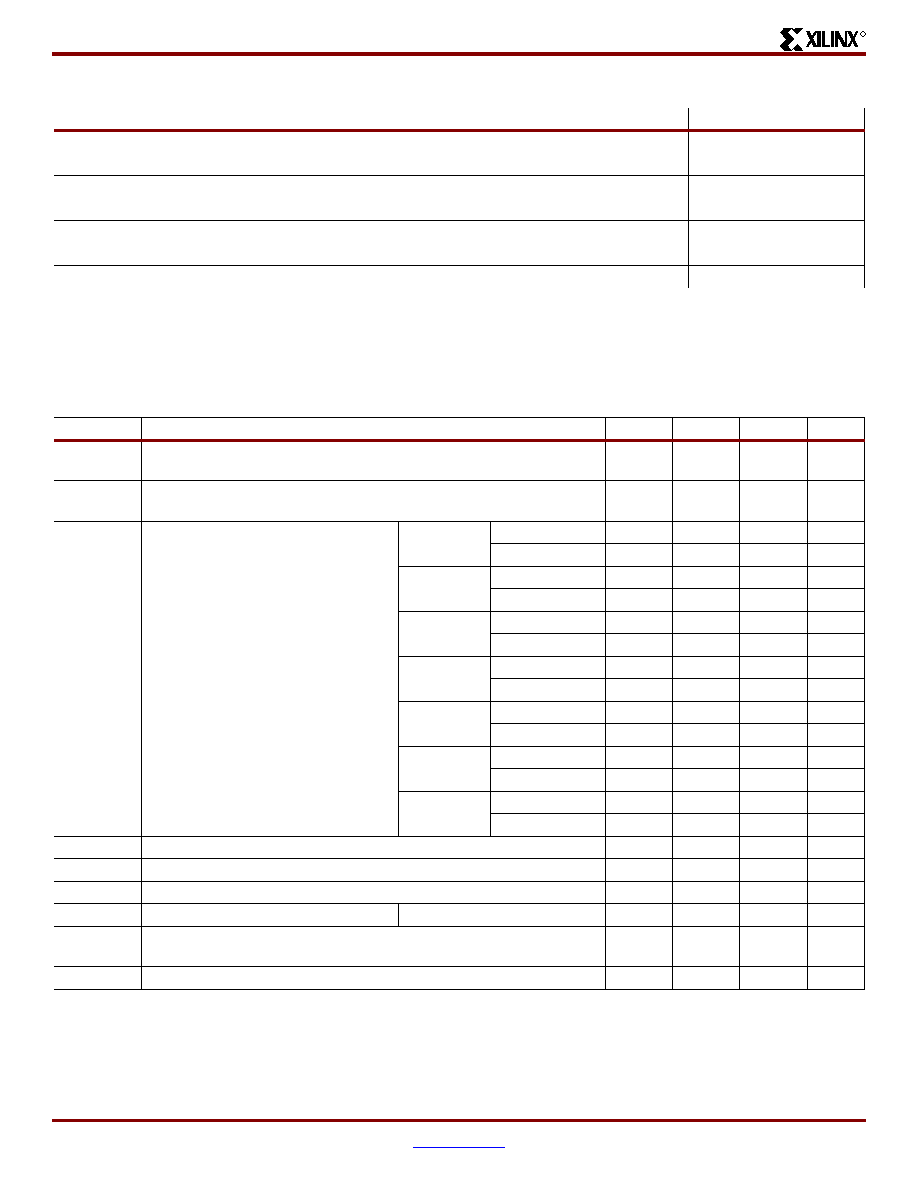

Recommended Operating Conditions

DC Characteristics Over Operating Conditions

Symbol

Description

Min

Max

Units

TJ

Junction temperature

Commercial

0

85

°C

Industrial

–40

100

°C

VCCINT

Supply voltage relative to GND(1)

Commercial

1.8 – 5%

1.8 + 5%

V

Industrial

1.8 – 5%

1.8 + 5%

V

VCCO

Supply voltage relative to GND(2)

Commercial

1.2

3.6

V

Industrial

1.2

3.6

V

TIN

Input signal transition time(3)

-

250

ns

Notes:

1.

Functional operation is guaranteed down to a minimum VCCINT of 1.62V (Nominal VCCINT –10%). For every 50 mV reduction in

VCCINT below 1.71V (nominal VCCINT –5%), all delay parameters increase by approximately 3%.

2.

Minimum and maximum values for VCCO vary according to the I/O standard selected.

3.

Input and output measurement threshold is ~50% of VCCO. See Delay Measurement Methodology, page 41 for specific details.

Symbol

Description

Min

Typ

Max

Units

VDRINT

Data retention VCCINT voltage (below which configuration data may

be lost)

1.5

-

V

VDRIO

Data retention VCCO voltage (below which configuration data may be

lost)

1.2

-

V

ICCINTQ

Quiescent VCCINT supply current(1)

XC2S50E

Commercial

-

10

200

mA

Industrial

-

10

200

mA

XC2S100E

Commercial

-

10

200

mA

Industrial

-

10

200

mA

XC2S150E

Commercial

-

10

300

mA

Industrial

-

10

300

mA

XC2S200E

Commercial

-

10

300

mA

Industrial

-

10

300

mA

XC2S300E

Commercial

-

12

300

mA

Industrial

-

12

300

mA

XC2S400E

Commercial

-

15

300

mA

Industrial

-

15

300

mA

XC2S600E

Commercial

-

15

400

mA

Industrial

-

15

400

mA

ICCOQ

Quiescent VCCO supply current(1)

-

2

mA

IREF

VREF current per VREF pin

-

20

μA

IL

Input or output leakage current per pin

–10

-

+10

μA

CIN

Input capacitance (sample tested)

TQ, PQ, FG, FT packages

-

8

pF

IRPU

Pad pull-up (when selected) @ VIN = 0V, VCCO = 3.3V

(sample tested)(2)

-

0.25

mA

IRPD

Pad pull-down (when selected) @ VIN = 3.6V (sample tested)(2)

-

0.25

mA

Notes:

1.

With no output current loads, no active input pull-up resistors, all I/O pins 3-stated and floating.

2.

Internal pull-up and pull-down resistors guarantee valid logic levels at unconnected input pins. These pull-up and pull-down resistors

do not provide valid logic levels when input pins are connected to other circuits.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| XC2S200E-6PQ208C | IC FPGA 1.8V 1176 CLB'S 208-PQFP |

| 747275-4 | CONN D-SUB STRAIN RELIEF 9POS |

| XC3S700A-5FTG256C | IC FPGA SPARTAN-3A 256K 256FTBGA |

| XA3S400-4PQG208Q | IC FPGA SPARTAN-3 400K 208-PQFP |

| EEC43DTEF | CONN EDGECARD 86POS .100 EYELET |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| XC2S200E-6PQG208I | 制造商:XILINX 制造商全稱:XILINX 功能描述:Spartan-IIE FPGA |

| XC2S200E-6TQ144C | 制造商:XILINX 制造商全稱:XILINX 功能描述:Spartan-IIE 1.8V FPGA Family |

| XC2S200E-6TQ144I | 制造商:XILINX 制造商全稱:XILINX 功能描述:Spartan-IIE 1.8V FPGA Family |

| XC2S200E-6TQG144C | 制造商:XILINX 制造商全稱:XILINX 功能描述:Spartan-IIE FPGA |

| XC2S200E-6TQG144I | 制造商:XILINX 制造商全稱:XILINX 功能描述:Spartan-IIE FPGA |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。