- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄4283 > XC2S200E-6PQ208C (Xilinx Inc)IC FPGA 1.8V 1176 CLB'S 208-PQFP PDF資料下載

參數(shù)資料

| 型號: | XC2S200E-6PQ208C |

| 廠商: | Xilinx Inc |

| 文件頁數(shù): | 51/108頁 |

| 文件大小: | 0K |

| 描述: | IC FPGA 1.8V 1176 CLB'S 208-PQFP |

| 標準包裝: | 24 |

| 系列: | Spartan®-IIE |

| LAB/CLB數(shù): | 1176 |

| 邏輯元件/單元數(shù): | 5292 |

| RAM 位總計: | 57344 |

| 輸入/輸出數(shù): | 146 |

| 門數(shù): | 200000 |

| 電源電壓: | 1.71 V ~ 1.89 V |

| 安裝類型: | 表面貼裝 |

| 工作溫度: | 0°C ~ 85°C |

| 封裝/外殼: | 208-BFQFP |

| 供應商設備封裝: | 208-PQFP(28x28) |

| 其它名稱: | 122-1209 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁當前第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁

DS077-3 (v3.0) August 9, 2013

47

Product Specification

Spartan-IIE FPGA Family: DC and Switching Characteristics

R

— OBSOLETE — OBSOLETE — OBSOLETE — OBSOLETE —

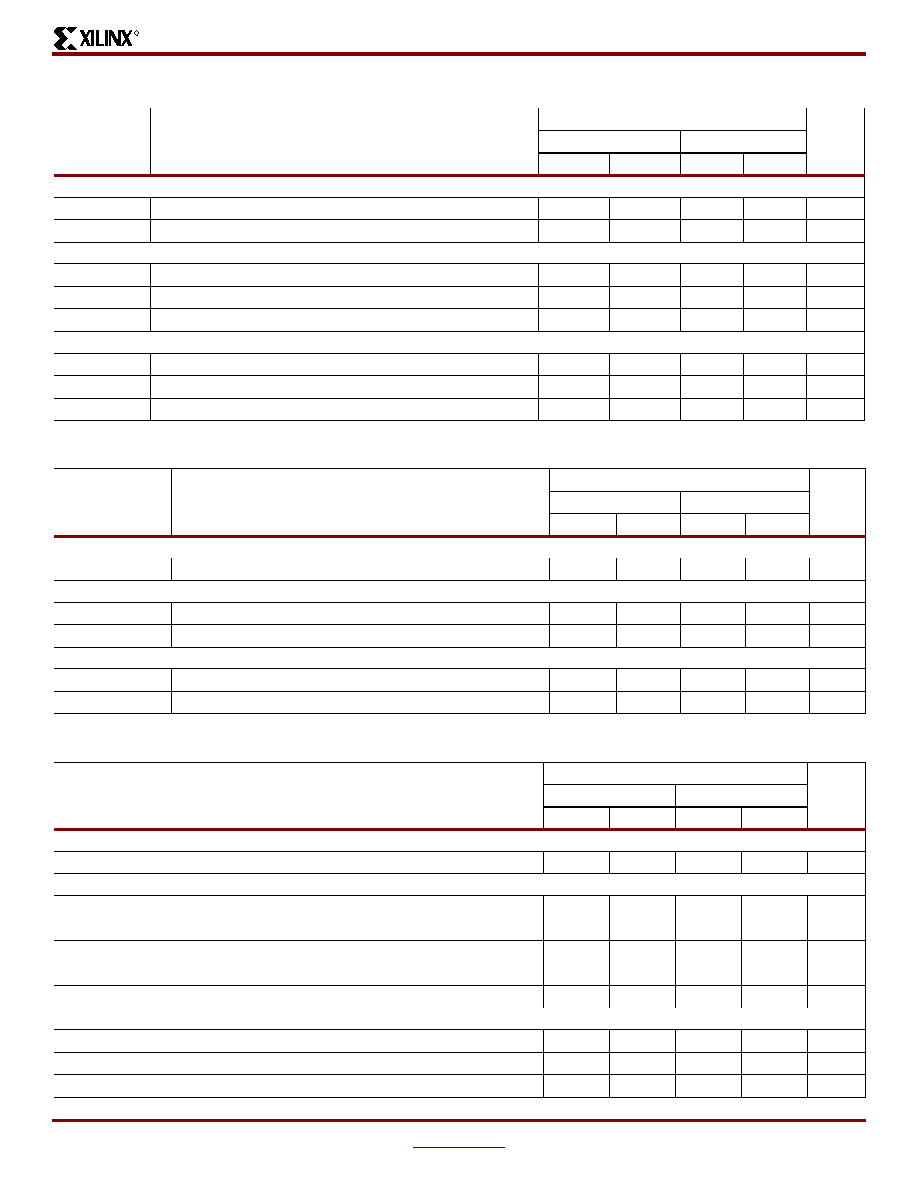

CLB Distributed RAM Switching Characteristics

CLB Shift Register Switching Characteristics

Block RAM Switching Characteristics

Symbol

Description

Speed Grade

Units

-7

-6

Min

Max

Min

Max

Sequential Delays

TSHCKO16

Clock CLK to X/Y outputs (WE active, 16 x 1 mode)

0.6

1.5

0.6

1.7

ns

TSHCKO32

Clock CLK to X/Y outputs (WE active, 32 x 1 mode)

0.8

1.9

0.8

2.1

ns

Setup/Hold Times with Respect to Clock CLK

TAS / TAH

F/G address inputs

0.42 / 0

-

0.5 / 0

-

ns

TDS / TDH

BX/BY data inputs (DIN)

0.53 / 0

-

0.6 / 0

-

ns

TWS / TWH

CE input (WS)

0.7 / 0

-

0.8 / 0

-

ns

Clock CLK

TWPH

Pulse width, High

2.1

-

2.4

-

ns

TWPL

Pulse width, Low

2.1

-

2.4

-

ns

TWC

Clock period to meet address write cycle time

4.2

-

4.8

-

ns

Symbol

Description

Speed Grade

Units

-7

-6

Min

Max

Min

Max

Sequential Delays

TREG

Clock CLK to X/Y outputs

1.2

2.9

1.2

3.2

ns

Setup/Hold Times with Respect to Clock CLK

TSHDICK

BX/BY data inputs (DIN)

0.53 / 0

-

0.6 / 0

-

ns

TSHCECK

CE input (WS)

0.7 / 0

-

0.8 / 0

-

ns

Clock CLK

TSRPH

Pulse width, High

2.1

-

2.4

-

ns

TSRPL

Pulse width, Low

2.1

-

2.4

-

ns

Symbol

Description

Speed Grade

Units

-7

-6

Min

Max

Min

Max

Sequential Delays

TBCKO

Clock CLK to DOUT output

0.6

3.1

0.6

3.5

ns

Setup/Hold Times with Respect to Clock CLK

TBACK / TBCKA

ADDR inputs

1.0 / 0

-

1.1 / 0

-

ns

TBDCK/ TBCKD

DIN inputs

1.0 / 0

-

1.1 / 0

-

ns

TBECK/ TBCKE

EN inputs

2.2 / 0

-

2.5 / 0

-

ns

TBRCK/ TBCKR

RST input

2.1 / 0

-

2.3 / 0

-

ns

TBWCK/ TBCKW

WEN input

2.0 / 0

-

2.2 / 0

-

ns

Clock CLK

TBPWH

Pulse width, High

1.4

-

1.5

-

ns

TBPWL

Pulse width, Low

1.4

-

1.5

-

ns

TBCCS

CLKA -> CLKB setup time for different ports

2.7

-

3.0

-

ns

相關PDF資料 |

PDF描述 |

|---|---|

| 747275-4 | CONN D-SUB STRAIN RELIEF 9POS |

| XC3S700A-5FTG256C | IC FPGA SPARTAN-3A 256K 256FTBGA |

| XA3S400-4PQG208Q | IC FPGA SPARTAN-3 400K 208-PQFP |

| EEC43DTEF | CONN EDGECARD 86POS .100 EYELET |

| 229910-1 | CONN CABLE CLAMP BLACK .350-.425 |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| XC2S200E-6PQ208I | 功能描述:IC FPGA 1.8V 1176 CLB'S 208-PQFP RoHS:是 類別:集成電路 (IC) >> 嵌入式 - FPGA(現(xiàn)場可編程門陣列) 系列:Spartan®-IIE 標準包裝:40 系列:Spartan® 6 LX LAB/CLB數(shù):3411 邏輯元件/單元數(shù):43661 RAM 位總計:2138112 輸入/輸出數(shù):358 門數(shù):- 電源電壓:1.14 V ~ 1.26 V 安裝類型:表面貼裝 工作溫度:-40°C ~ 100°C 封裝/外殼:676-BGA 供應商設備封裝:676-FBGA(27x27) |

| XC2S200E-6PQG208C | 功能描述:IC SPARTAN-IIE FPGA 200K 208PQFP RoHS:是 類別:集成電路 (IC) >> 嵌入式 - FPGA(現(xiàn)場可編程門陣列) 系列:Spartan®-IIE 標準包裝:40 系列:Spartan® 6 LX LAB/CLB數(shù):3411 邏輯元件/單元數(shù):43661 RAM 位總計:2138112 輸入/輸出數(shù):358 門數(shù):- 電源電壓:1.14 V ~ 1.26 V 安裝類型:表面貼裝 工作溫度:-40°C ~ 100°C 封裝/外殼:676-BGA 供應商設備封裝:676-FBGA(27x27) |

| XC2S200E-6PQG208I | 制造商:XILINX 制造商全稱:XILINX 功能描述:Spartan-IIE FPGA |

| XC2S200E-6TQ144C | 制造商:XILINX 制造商全稱:XILINX 功能描述:Spartan-IIE 1.8V FPGA Family |

| XC2S200E-6TQ144I | 制造商:XILINX 制造商全稱:XILINX 功能描述:Spartan-IIE 1.8V FPGA Family |

發(fā)布緊急采購,3分鐘左右您將得到回復。