- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄372532 > X25385 Selectable Timeout Watchdog & V CC Supervisory Circuit w/Serial E 3 PROM(可選超時(shí)看門狗監(jiān)控電路) PDF資料下載

參數(shù)資料

| 型號: | X25385 |

| 英文描述: | Selectable Timeout Watchdog & V CC Supervisory Circuit w/Serial E 3 PROM(可選超時(shí)看門狗監(jiān)控電路) |

| 中文描述: | 可選的超時(shí)看門狗 |

| 文件頁數(shù): | 4/15頁 |

| 文件大小: | 90K |

| 代理商: | X25385 |

X25383/85

4

ues, the counter will roll back to the first address of the

same page and overwrite any data that may have been

previously written.

For a Write Operation (byte or page write) to be com-

pleted, CS can only be brought HIGH after bit 0 of the last

data byte to be written is clocked in. If it is brought HIGH

at any other time, the write operation will not be com-

pleted (Figure 4).

To write to the Status Register, the WRSR instruction is

followed by the data to be written (Figure 5). Data bits 5, 6

and 7 must be “0” .

Read Status Operation

If there is not a nonvolatile write in progress, the Read

Status instruction returns the ID Lock byte from the Status

Register which contains the ID Lock bits IDL2-IDL0 (Fig-

ure 1). The ID Lock bits define the ID Lock condition (Fig-

ure 1/Table1). The other bits are reserved and will return

’0’ when read. See Figure 3.

If a nonvolatile write is in progress, the Read Status

Instruction returns a HIGH on SO. When the nonvolatile

write cycle is completed, the status register data is read

out.

Clocking SCK is valid during a nonvolatile write in

progress, but is not necessary. If the SCK line is clocked,

the pointer to the status register is also clocked, even

though the SO pin shows the status of the nonvolatile

write operation (See Figure 3).

RESET/RESET Operation

The RESET (X25383) output is designed to go LOW

whenever V

CC

has dropped below the minimum trip point

and/or the Watchdog timer has reached its programmable

time-out limit.

The RESET (X25385) output is designed to go HIGH

whenever V

CC

has dropped below the minimum trip point

and/or the watchdog timer has reached its programmable

time-out limit.

The RESET/RESET output is an open drain output and

requires a pull up resistor.

Operational Notes

The device powers-up in the following state:

The device is in the low power standby state.

A HIGH to LOW transition on CS is required to enter an

active state and receive an instruction.

SO pin is high impedance.

The Write Enable Latch is reset.

Reset Signal is active for t

PURST

.

Data Protection

The following circuitry has been included to prevent inad-

vertent writes:

A WREN instruction must be issued to set the Write

Enable Latch.

CS must come HIGH at the proper clock count in order

to start a nonvolatile write cycle.

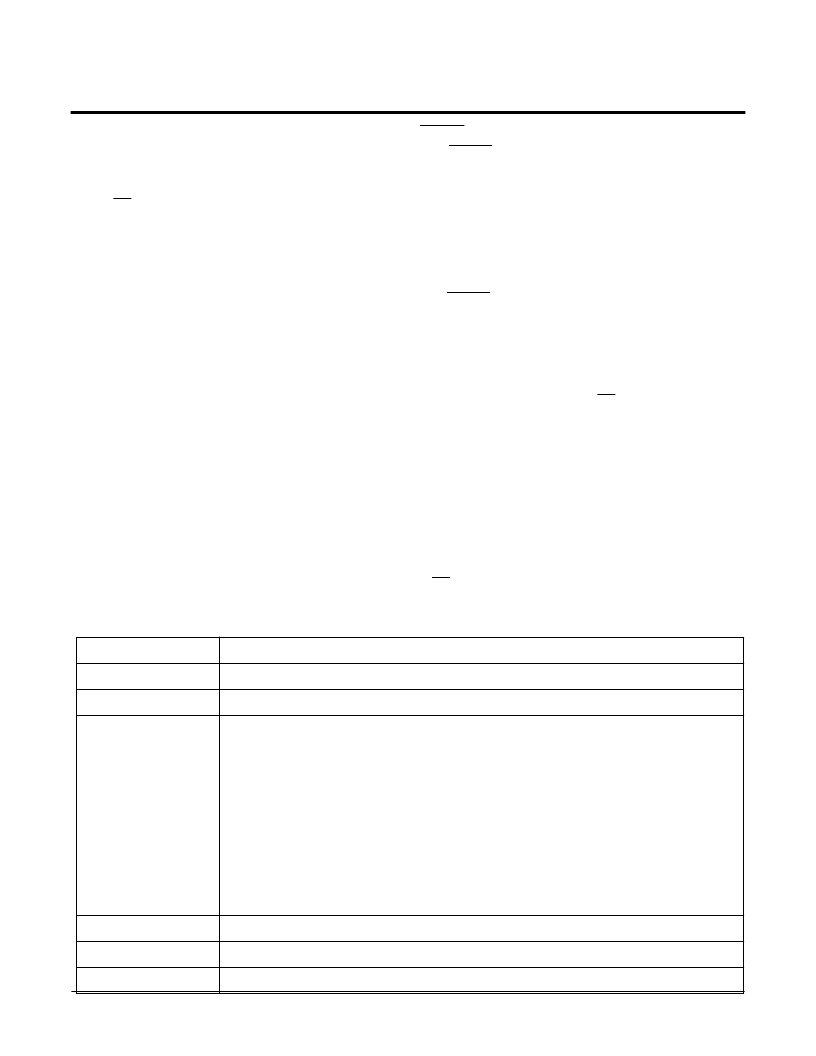

Table 1. Instruction Set and IDLock Protection Byte Definition

Instruction Format*

Instruction Name and Operation

0000 0110

WREN: Set the Write Enable Latch (Write Enable Operation)

0000 0100

WRDI: Reset the Write Enable Latch (Write Disable Operation)

0000 0001

Write Status Instruction—followed by:

IDLock/WDT Byte: (See Figure 1)

000W

1

W

2

000 --->NO IDLock: 00h-00h - - - - - - - >None of the Array

000W

1

W

2

001 --->IDLock Q1: 0000h-00FFh - - - - >Lower Quadrant (Q1)

000W

1

W

2

010 --->IDLock Q2: 0100h-01FFh - - - - >Q2

000W

1

W

2

011 --->IDLock Q3: 0200h-02FFh - - - - >Q3

000W

1

W

2

100 --->IDLock Q4: 0300h-03FFh - - - - >Upper Quadrant (Q4)

000W

1

W

2

101 --->IDLock H1: 0000h-01FFh - - - - >Lower Half of the Array (H1)

000W

1

W

2

110 --->IDLock P0: 0000h-000Fh - - - - >Lower Page (P0)

000W

1

W

2

111 --->IDLock Pn: 03F0h-03FFh - - - - >Upper Page (Pn)

0000 0101

READ STATUS: Reads Status Register & provides write in progress status on SO Pin

0000 0010

WRITE: Write operation followed by address and data

0000 0011

READ: Read operation followed by address

W0=WD0Bit

Note:

W1=WD1Bit

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| X25640S | IC-SM-64K SERIAL EEPROM+SPI |

| X25330S8 | SPI Serial EEPROM |

| X25330S8I | SPI Serial EEPROM |

| X25330S8I-2.5 | SPI Serial EEPROM |

| X25640 | Advanced SPI Serial E2PROM With Block LockTM Protection |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| X25385S8 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:SPI Serial EEPROM with Supervisory Features |

| X25385S8-1.8 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:SPI Serial EEPROM with Supervisory Features |

| X25385S8-2.7 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:SPI Serial EEPROM with Supervisory Features |

| X25385S8I | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:SPI Serial EEPROM with Supervisory Features |

| X25385S8I-1.8 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:SPI Serial EEPROM with Supervisory Features |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。