- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄372526 > X1203 2-Wire RTC(Real Time Clock)/Calendar/Alarm(實(shí)時(shí)時(shí)鐘/日歷/警報(bào)) PDF資料下載

參數(shù)資料

| 型號(hào): | X1203 |

| 英文描述: | 2-Wire RTC(Real Time Clock)/Calendar/Alarm(實(shí)時(shí)時(shí)鐘/日歷/警報(bào)) |

| 中文描述: | 2線實(shí)時(shí)時(shí)鐘(實(shí)時(shí)時(shí)鐘)/日歷/鬧鐘(實(shí)時(shí)時(shí)鐘/日歷/警報(bào)) |

| 文件頁(yè)數(shù): | 5/19頁(yè) |

| 文件大?。?/td> | 84K |

| 代理商: | X1203 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)當(dāng)前第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)

X1203

5

REAL TIME CLOCK REGISTERS

Year 2000 (Y2K)

The X1203 has a century byte that “rolls over” from 19

to 20 when the years byte changes from 99 to 00. The

Y2K byte can contain only the values of 19 or 20.

Day of the Week Register (DW)

This register provides a Day of the Week status and

uses three bits DY2 to DY0 to represent the seven days

of the week. The counter advances in the cycle 0-1-2-3-

4-5-6-0-1-2-... The assignment of a numerical value to

a specific day of the week is arbitrary and may be

decided by the system software designer. The Clock

Default values define 0=Sunday.

Clock/Calendar Registers (YR, MO, DT, HR, MN, SC)

These registers depict BCD representations of the time.

As such, SC (Seconds) and MN (Minutes) range from

00 to 59, HR (Hour) is 1 to 12 with an AM or PM indica-

tor (H21 bit) or 0 to 23 (with T24=1), DT (Date) is 1 to

31, MO (Month) is 1 to 12, YR (year) is 0 to 99.

24 Hour Time

If the T24 bit of the HR register is 1, the RTC will use a

24-hour format. If the T24 bit is 0, the RTC will use 12-

hour format and bit H21 will function as an AM/PM indi-

cator with a ‘1’ representing PM. The clock defaults to

Standard Time with H21=0.

Leap Years

Leap years add the day February 29 and are defined as

those years that are divisible by 4. Years divisible by

100 are not leap years, unless they are also divisible by

400. This means that the year 2000 is a leap year, the

year 2100 is not. The X1203 does not correct for the

leap year in the year 2100.

STATUS REGISTER (SR)

The Status Register is located in the RTC area at

address 003FH. This is a volatile register only and is

used to control the WEL and RWEL write enable

latches, read an optional Low Voltage Sense bit, and

read the two alarm bits. This register is logically seper-

ated from both the array and the Clock/Control Regis-

ters (CCR).

BAT: Battery Supply—Volatile

This bit set to “1” indicates that the device is operating

from V

BACK

, not V

CC

. It is a read only bit and is set/

reset by hardware.

AL1, AL0: Alarm bits—Volatile

These bits announce if either alarm 1 or alarm 2 match

the real time clock. If there is a match, the respective bit

is set to ‘1’. The falling edge of the last data bit in a SR

Read operation resets the flags. Note: Only the AL bits

that are set when an SR read starts will be reset. An

alarm bit that is set by an alarm occuring during an SR

read operation will remain set after the read operation

is complete.

RWEL: Register Write Enable Latch—Volatile

This bit is a volatile latch that powers up in the LOW

(disabled) state. The RWEL bit must be set to “1” prior

to any writes to the Clock/Control Registers. Writes to

RWEL bit do not cause a nonvolatile write cycle, so the

device is ready for the next operation immediately after

the stop condition. A write to the CCR requires both the

RWEL and WEL bits to be set in a specific sequence.

WEL: Write Enable Latch—Volatile

The WEL bit controls the access to the CCR during a

write operation. This bit is a volatile latch that powers

up in the LOW (disabled) state. While the WEL bit is

LOW, writes to the CCR or any array address will be

ignored (no acknowledge will be issued after the Data

Byte). The WEL bit is set by writing a “1” to the WEL bit

and zeroes to the other bits of the Status Register.

Once set, WEL remains set until either reset to 0 (by

writing a “0” to the WEL bit and zeroes to the other bits

of the Status Register) or until the part powers up

again. Writes to WEL bit do not cause a non volatile

write cycle, so the device is ready for the next operation

immediately after the stop condition.

RTCF: Real Time Clock Fail Bit—Volatile

This bit is set to a ‘1’ after a total power failure. This is a

read only bit that is set by hardware when the device

powers up after having lost all power to the device. The

bit is set regardless of whether V

first. The loss of one or the other supplies does not

result in setting the RTCF bit. The first valid write to the

RTC (writing one byte is sufficient) resets the RTCF bit

to ‘0’.

CC

or V

BACK

is applied

Unused Bits:

These devices do not use bits 3 or 4, but must have a

zero in these bit positions. The Data Byte output during

a SR read will contain zeros in these bit locations.

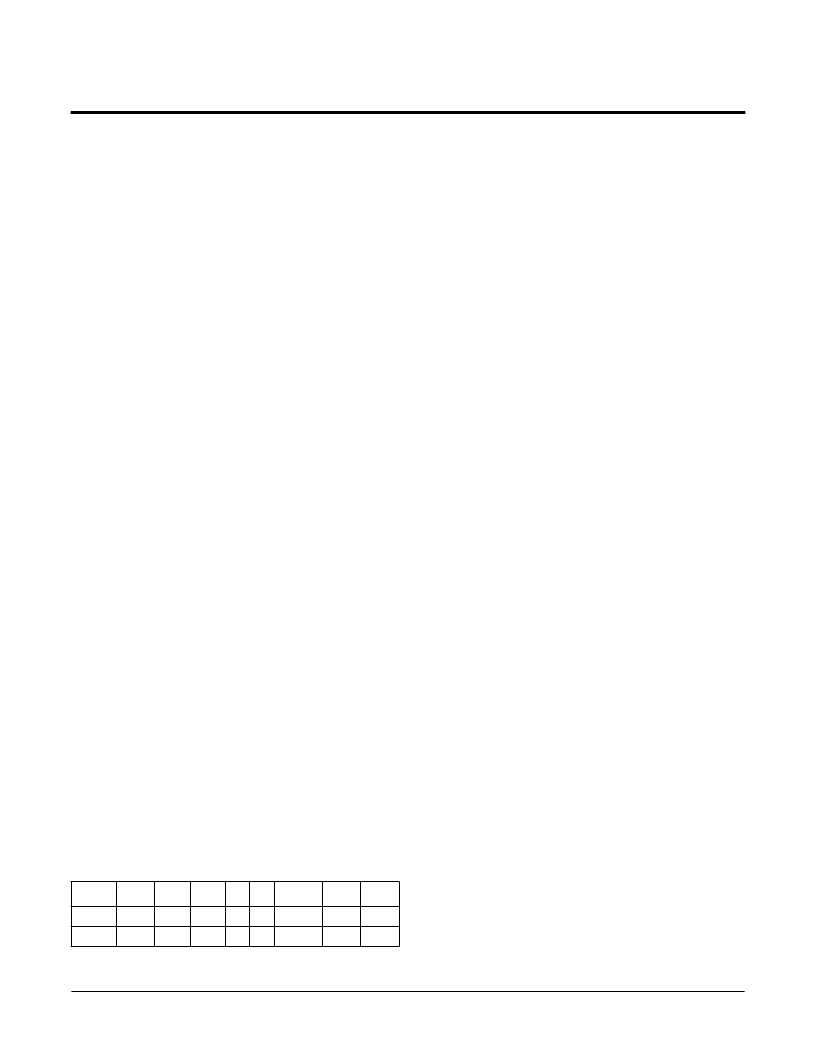

Table 2. Status Register (SR)

Addr

7

6

5

4

3

2

1

0

003Fh

Default

BAT

0

AL1

0

AL0

0

0

0

0

0

RWEL

0

WEL RTCF

0

0

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| x1205(中文) | Real Time Clock/Calendar(實(shí)時(shí)時(shí)鐘/日期) |

| X1205V8 | Real Time Clock/Calendar |

| X1205V8I | Real Time Clock/Calendar |

| X1205 | Real Time Clock/Calendar |

| X1205S8 | Real Time Clock/Calendar |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| X1203S8 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:IC-SMD-RTC WITH EEPROM |

| X1203S8I | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Real-Time Clock |

| X1203V8 | 制造商:Intersil Corporation 功能描述: |

| X-120-499 | 制造商:Brady Corporation 功能描述:VIAL SIDE/TOP COMBO-B499 .50X1X.375DIA |

| X1205 | 制造商:XICOR 制造商全稱:Xicor Inc. 功能描述:Real Time Clock/Calendar |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。