- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄300102 > VSP2582RHNR (TEXAS INSTRUMENTS INC) SPECIALTY ANALOG CIRCUIT, PQCC36 PDF資料下載

參數(shù)資料

| 型號(hào): | VSP2582RHNR |

| 廠商: | TEXAS INSTRUMENTS INC |

| 元件分類: | 模擬信號(hào)調(diào)理 |

| 英文描述: | SPECIALTY ANALOG CIRCUIT, PQCC36 |

| 封裝: | GREEN, PLASTIC, QFN-36 |

| 文件頁(yè)數(shù): | 8/22頁(yè) |

| 文件大小: | 435K |

| 代理商: | VSP2582RHNR |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)當(dāng)前第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)

SBES002A – JUNE 2008 – REVISED SEPTEMBER 2008................................................................................................................................................. www.ti.com

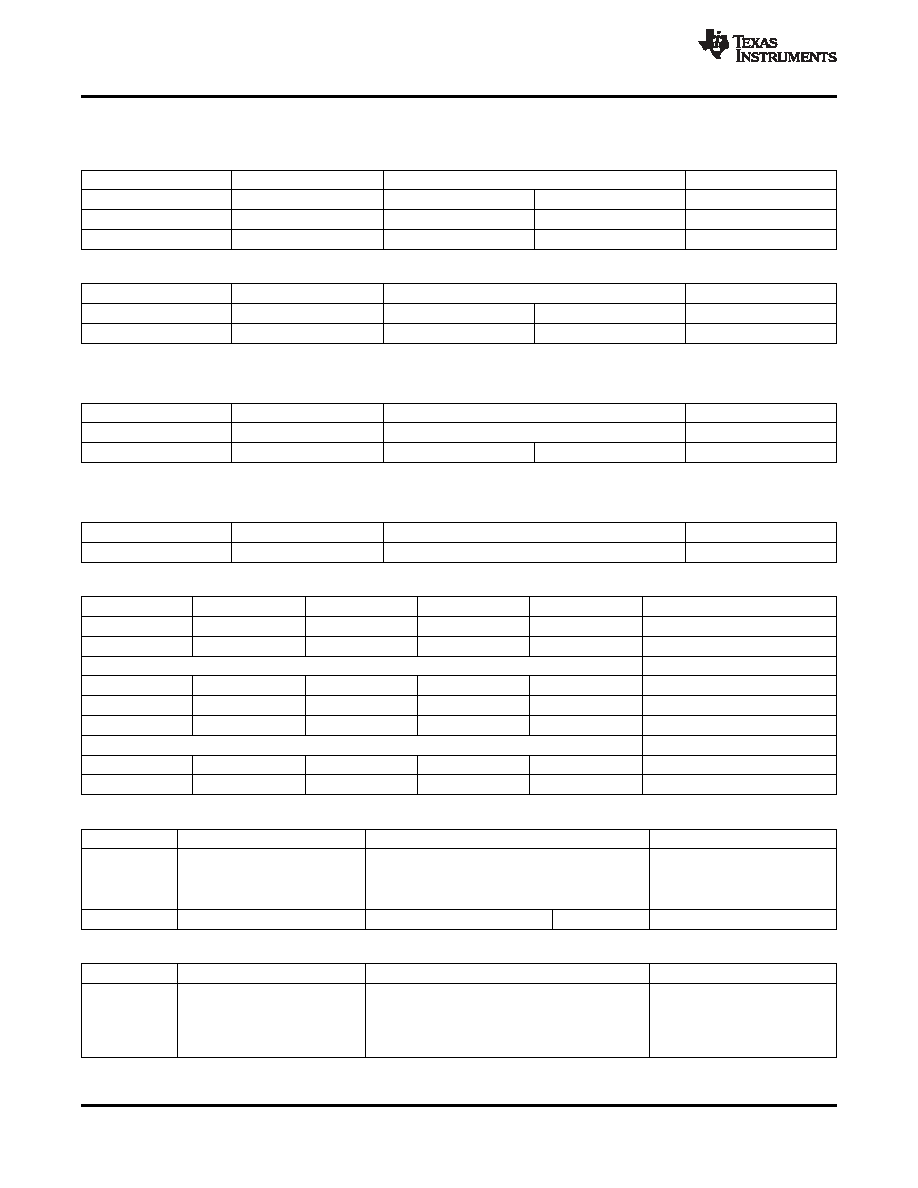

Clk-Pol-ctrl Register (Address: h000)

Clk-Pol-ctrl selects the active polarity of CLPDM, CLPOB, and SHP/SHD.

DATA BIT

NAME

DESCRIPTION

DEFAULT

D3

CLPDM Polarity

0 : Active Low

1 : Active High

0

D4

CLPOB Polarity

0 : Active Low

1 : Active High

0

D5

SHP/SHD Polarity

0 : Active Low

1 : Active High

0

AFE-ctrl(1) Register (Address: h001)

DATA BIT

NAME

DESCRIPTION

DEFAULT

D0

Standby

0: Normal operation

1: standby

0

D3

Test enable

0: disable

1: enable

0

AFE-ctrl(2) Register (Address: h002)

AFE-ctrl(2) register controls the following data output settings.

DATA BIT

NAME

DESCRIPTION

DEFAULT

D[1:0]

Data output delay

00: 0 ns, 01: 2 ns, 10: 4 ns, 11: 6 ns

0

D4

Output enable

0: enable

1: Hi-Z

0

S-delay Register (Address: h003)

S-delay register controls SHD sampling start time from the rising edge or SHP.

DATA BIT

NAME

DESCRIPTION

DEFAULT

D[1:0]

Sampling delay for SHD

00: 0 ns, 01: 2 ns (10, 11 are not allowed)

0

Clamp Register (Address: h004)

D4

D3

D2

D1

D0

CLAMP LEVEL (VSP2582)

0

64 LSB

0

1

72 LSB

:

0

1

120 LSB

0

1

0

128 LSB (default)

0

1

0

1

136 LSB

:

1

0

304 LSB

1

312 LSB

Hot-pixel Register (Address: h005)

DATA BIT

NAME

DESCRIPTION

DEFAULT

Hot pixel rejection level is givens following

equation.

D[4:0]

Hot pixel rejection level

11111

RL (LSB) = 16 (d[4:0] + 1)

Where: RL is level difference from OB level.

D5

Hot pixel rejection disable

0: disable

1: enable

1

D-PGA Register (Address: h006 and h007)

D-PGA_U

D-PGA_L

ANALOG GAIN

DEFAULT

Digital PGA gain is givens following equation.

Gain (dB) = (D-PGA 0.03125 ) – 6

D[3:0]

D[5:0]

Where: D-PGA is decimal value of 10-bit data

D-PGA = 00 1100 000 = 0 dB

which is combined D-PGA_U and D-PGA_L.

D-PGA_U is MSB side of D-PGA.

16

Copyright 2008, Texas Instruments Incorporated

Product Folder Link(s): VSP2582

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| VSPLD53TED1-669.3265 | VOLTAGE CONTROLLED CLOCK SAW OSCILLATOR, 669.3265 MHz |

| VSPM634D-644.5313MHZ | VOLTAGE CONTROLLED CLOCK SAW OSCILLATOR, 644.5313 MHz |

| VT048A015T100TP | 1-OUTPUT 161 W DC-DC REG PWR SUPPLY MODULE |

| VT048A015T100FP | 1-OUTPUT 161 W DC-DC REG PWR SUPPLY MODULE |

| VT048A080T030TP | 1-OUTPUT DC-DC REG PWR SUPPLY MODULE |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| VSP2582RHNRG4 | 功能描述:模數(shù)轉(zhuǎn)換器 - ADC 12B 36MHz AFE for DVC RoHS:否 制造商:Texas Instruments 通道數(shù)量:2 結(jié)構(gòu):Sigma-Delta 轉(zhuǎn)換速率:125 SPs to 8 KSPs 分辨率:24 bit 輸入類型:Differential 信噪比:107 dB 接口類型:SPI 工作電源電壓:1.7 V to 3.6 V, 2.7 V to 5.25 V 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:VQFN-32 |

| VSP2590 | 制造商:TI 制造商全稱:Texas Instruments 功能描述:DUAL-CHANNEL IMAGE SENSOR ANALOG FRONT-END |

| VSP2590ZWV | 功能描述:視頻模擬/數(shù)字化轉(zhuǎn)換器集成電路 16B 41.5MSPS 2Ch AFE For CCD Sensors RoHS:否 制造商:Texas Instruments 輸入信號(hào)類型:Differential 轉(zhuǎn)換器數(shù)量:1 ADC 輸入端數(shù)量:4 轉(zhuǎn)換速率:3 Gbps 分辨率:8 bit 結(jié)構(gòu): 輸入電壓:3.3 V 接口類型:SPI 信噪比: 電壓參考: 電源電壓-最大:3.45 V 電源電壓-最小:3.15 V 最大功率耗散: 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 封裝 / 箱體:TCSP-48 封裝:Reel |

| VSP2590ZWVR | 功能描述:視頻模擬/數(shù)字化轉(zhuǎn)換器集成電路 16B 41.5MSPS 2Ch AFE For CCD Sensors RoHS:否 制造商:Texas Instruments 輸入信號(hào)類型:Differential 轉(zhuǎn)換器數(shù)量:1 ADC 輸入端數(shù)量:4 轉(zhuǎn)換速率:3 Gbps 分辨率:8 bit 結(jié)構(gòu): 輸入電壓:3.3 V 接口類型:SPI 信噪比: 電壓參考: 電源電壓-最大:3.45 V 電源電壓-最小:3.15 V 最大功率耗散: 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 封裝 / 箱體:TCSP-48 封裝:Reel |

| VSP3000 | 制造商:BB 制造商全稱:BB 功能描述:12-Bit, 6MHz CCD/CIS SIGNAL PROCESSOR |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。