- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄202451 > VG26VS17405DJ-5 (VANGUARD INTERNATIONAL SEMICONDUCTOR CORP) 4M X 4 EDO DRAM, 50 ns, PDSO24 PDF資料下載

參數(shù)資料

| 型號(hào): | VG26VS17405DJ-5 |

| 廠商: | VANGUARD INTERNATIONAL SEMICONDUCTOR CORP |

| 元件分類: | DRAM |

| 英文描述: | 4M X 4 EDO DRAM, 50 ns, PDSO24 |

| 封裝: | 0.300 INCH, PLASTIC, SOJ-26/24 |

| 文件頁(yè)數(shù): | 2/27頁(yè) |

| 文件大?。?/td> | 253K |

| 代理商: | VG26VS17405DJ-5 |

第1頁(yè)當(dāng)前第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)

Document:1G5-0124

Rev.1

Page 10

VIS VG26(V)(S)17405

4,194,304 x 4 - Bit

CMOS Dynamic RAM

AC Characteristics

(

Ta = 0 to + 70°C, Vcc = 5V

% or 3.3V

%, Vss = 0V) *1, *2, *3, *4

Test conditions

Output load: two TTL Loads and 100pF (VCC = 5.0V

%)

one TTL Load and 100pF (VCC = 3.3V

%)

Input timing reference levels:

VIH = 2.4V, VIL = 0.8V (VCC = 5.0V

%); VIH = 2.0V, VIL = 0.8V (VCC = 3.3V

%)

Output timing reference levels:

VOH = 2.0V, VOL = 0.8V (VCC = 5V

%, 3.3V

%)

10

±

10

±

10

±

10

±

10

±

10

±

10

±

10

±

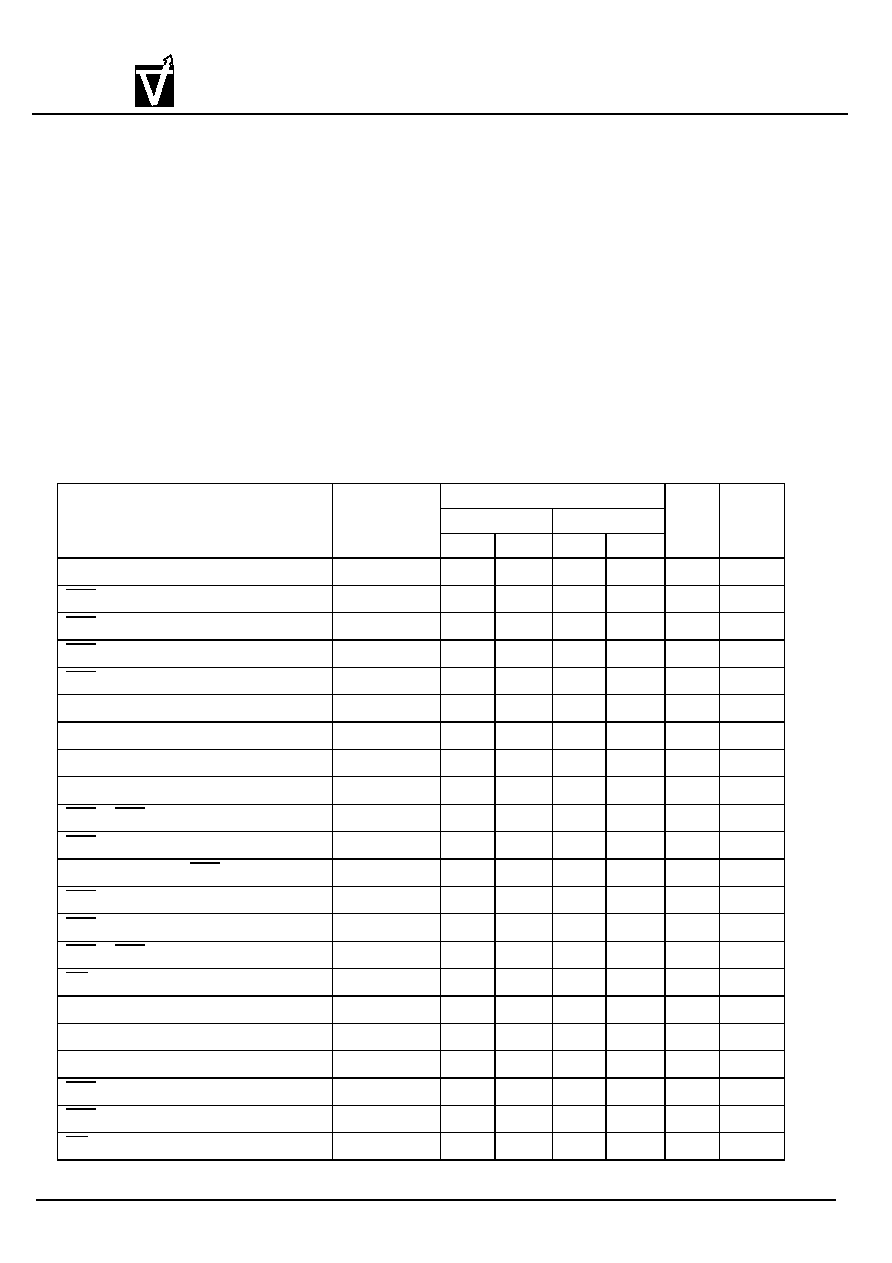

Read, Write, Read- Modify- Write and Refresh Cycles

(Common Parameters)

Parameter

Symbol

VG26(V)(S) 17405

Unit

Notes

-5

-6

Min

Max

Min

Max

Random read or write cycle time

tRC

84

-

104

-

ns

RAS precharge time

tRP

30

-

40

-

ns

CAS precharge time in normal mode

tCPN

10

-

10

-

ns

RAS pulse width

tRAS

50

10000

60

10000

ns

5

CAS pulse width

tCAS

8

10000

10

10000

ns

6

Row address setup time

tASR

0

-

0

-

ns

Row address hold time

tRAH

8

-

10

-

ns

Column address setup time

tASC

0

-

0

-

ns

7

Column address hold time

tCAH

8

-

10

-

ns

RAS to CAS delay time

tRCD

12

37

14

45

ns

8

RAS to column address delay time

tRAD

10

25

12

30

ns

9

Column address to RAS lead time

tRAL

25

-

30

-

ns

RAS hold time

tRSH

8

-

10

-

ns

CAS hold time

tCSH

38

-

40

-

ns

CAS to RAS precharge time

tCRP

5

-

5

-

ns

10

OE to Din delay time

tOED

12

-

15

-

ns

Transition time (rise and fall)

tT

1

50

1

50

ns

11

Refresh period

tREF

-

32

-

32

ms

Refresh period (S- Version)

tREF

-

128

-

128

ms

CAS to output in Low- Z

tCLZ

0

-

0

-

ns

CAS delay time from Din

tDZC

0

-

0

-

ns

OE delay time from Din

tDZO

0

-

0

-

ns

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| VG26VS17405DT-5 | 4M X 4 EDO DRAM, 50 ns, PDSO24 |

| VG26VS17405J-5 | 4M X 4 EDO DRAM, 50 ns, PDSO24 |

| VG36128161BFL-7H | 8M X 16 SYNCHRONOUS DRAM, 5.4 ns, PBGA54 |

| VG36128161BT-7H | 8M X 16 SYNCHRONOUS DRAM, 5.4 ns, PDSO54 |

| VG36128161BFL-7L | 8M X 16 SYNCHRONOUS DRAM, 5.4 ns, PBGA54 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| VG26VS17405DJ-6 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:DRAM|EDO|4MX4|CMOS|SOJ|26PIN|PLASTIC |

| VG26VS17405DT-5 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:x4 EDO Page Mode DRAM |

| VG26VS17405DT-6 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:x4 EDO Page Mode DRAM |

| VG26VS17405EJ-5 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:x4 EDO Page Mode DRAM |

| VG26VS17405EJ-6 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:x4 EDO Page Mode DRAM |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。