- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄202173 > V59C1G01408QAUP5E (PROMOS TECHNOLOGIES INC) 256M X 4 DDR DRAM, BGA68 PDF資料下載

參數(shù)資料

| 型號: | V59C1G01408QAUP5E |

| 廠商: | PROMOS TECHNOLOGIES INC |

| 元件分類: | DRAM |

| 英文描述: | 256M X 4 DDR DRAM, BGA68 |

| 封裝: | GREEN, FBGA-68 |

| 文件頁數(shù): | 74/79頁 |

| 文件大小: | 1028K |

| 代理商: | V59C1G01408QAUP5E |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁當前第74頁第75頁第76頁第77頁第78頁第79頁

76

V59C1G01(408/808/168)QA Rev. 1.3 June 2008

ProMOS TECHNOLOGIES

V59C1G01(408/808/168)QA

Reference Loads, Slew Rates and Slew Rate Derating

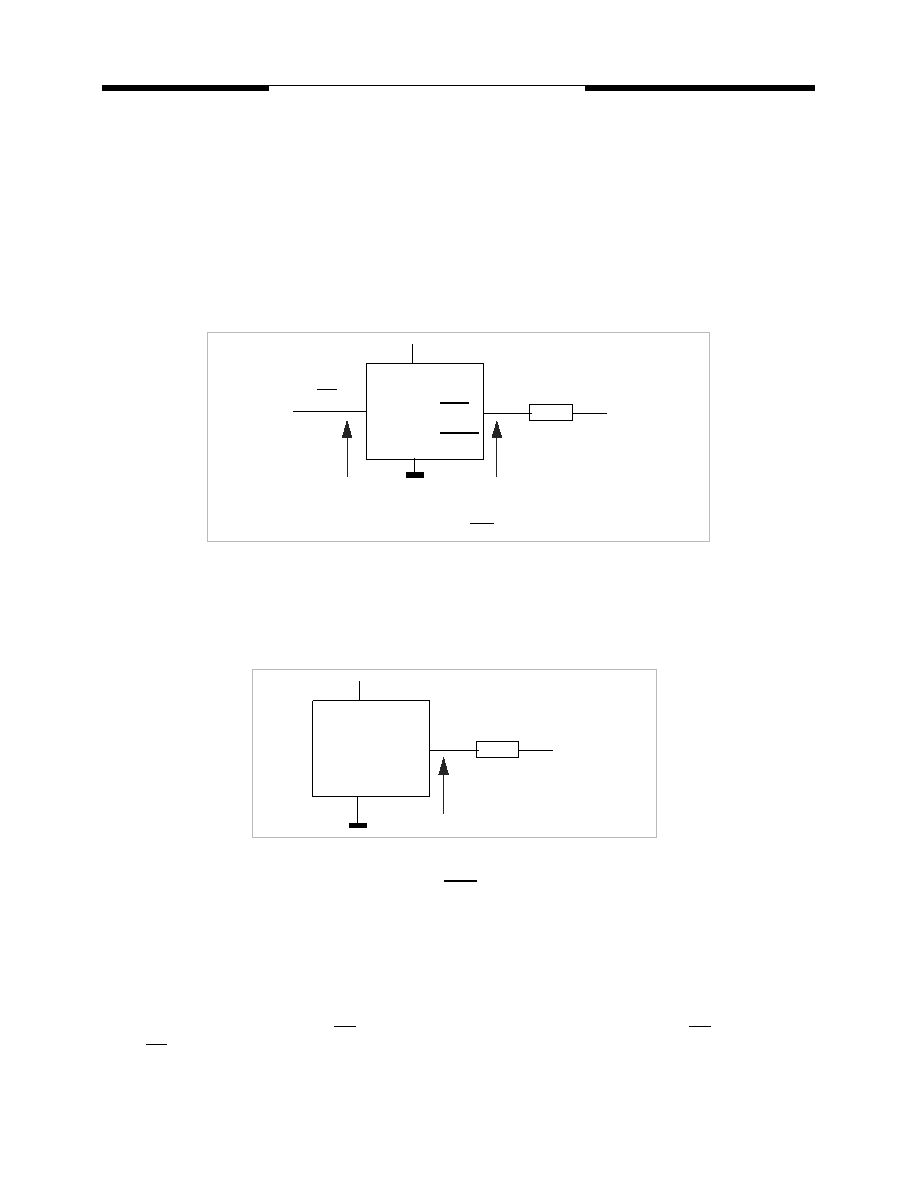

Reference Load for Timing Measurements

The figure represents the timing reference load used in defining the relevant timing parameters of the device.

It is not intended to either a precise representation of the typical system environment nor a depiction of the

actual load presented by a production tester. System designers will use IBIS or other simulation tools to cor-

relate the timing reference load to a system environment. This load circuit is also used for output slew rate

measurements.

25 Ohm

Vtt = VDDQ / 2

CK, CK

DUT

Timing Reference Points

VDDQ

DQ

DQS

RDQS

Note: The output timing reference voltage level for single ended signals is the crosspoint with VTT.

The output timing reference voltage level for differential signals is the crosspoint of the

true (e.g. DQS) and the complement (e.g. DQS) signal.

Slew Rate Measurements

Output Slew Rate

Output slew rate is characterized under the test conditions as shown in the figure below

25 Ohm

Vtt = VDDQ / 2

DUT

Test Point

VDDQ

DQ

DQS

RDQS

Output slew rate for falling and rising edges is measured between VTT - 250 mV and VTT + 250 mV for single

ended signals.For differential signals (e.g. DQS - DQS) output slew rate is measured between DQS - DQS =

- 500 mV and DQS - DQS = + 500 mV.Output slew rate is guaranteed by design, but is not necessarilty tested

on each device.

Input Slew Rate

Input slew for single ended signals is measured from dc-level to ac-level from VREF to VIH(AC),min for rising

and from VREF to VIL(AC), min or falling edges.

For differential signals (e.g. CK - CK) slew rate for rising edges is measured from CK - CK = -250 mV to

CK -CK = +500 mV (250 mV to -500 mV for falling edges). Test conditions are the same as for timing mea-

surements.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| V59C1G01804QALF19 | 128M X 8 DDR DRAM, PBGA68 |

| V59C1G01804QALF25A | 128M X 8 DDR DRAM, PBGA68 |

| V59C1G01804QAUJ19AH | 128M X 8 DDR DRAM, PBGA68 |

| V59C1G01804QAUJ25AI | 128M X 8 DDR DRAM, PBGA68 |

| V59C1G01808QALF19E | 128M X 8 DDR DRAM, BGA68 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| V5A010CB | 制造商:Honeywell Sensing and Control 功能描述:MICROSWITCH V5 PIN PLUNGER |

| V5A010CB | 制造商:Honeywell Sensing and Control 功能描述:MICROSWITCH V5 PIN PLUNGER |

| V5A010CB4D | 制造商:Honeywell Sensing and Control 功能描述:MICROSWITCH V5 ROLLER LEVER |

| V5A010CB4D | 制造商:Honeywell Sensing and Control 功能描述:MICROSWITCH V5 ROLLER LEVER |

| V5A010CB4E | 制造商:Honeywell Sensing and Control 功能描述:MICROSWITCH V5 ROLLER LEVER |

發(fā)布緊急采購,3分鐘左右您將得到回復。