- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄202173 > V59C1G01408QAUP5E (PROMOS TECHNOLOGIES INC) 256M X 4 DDR DRAM, BGA68 PDF資料下載

參數(shù)資料

| 型號(hào): | V59C1G01408QAUP5E |

| 廠商: | PROMOS TECHNOLOGIES INC |

| 元件分類: | DRAM |

| 英文描述: | 256M X 4 DDR DRAM, BGA68 |

| 封裝: | GREEN, FBGA-68 |

| 文件頁數(shù): | 29/79頁 |

| 文件大?。?/td> | 1028K |

| 代理商: | V59C1G01408QAUP5E |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁當(dāng)前第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁

35

ProMOS TECHNOLOGIES

V59C1G01(408/808/168)QA

V59C1G01(408/808/168)QA Rev. 1.3 June 2008

Burst Interruption

Interruption of a read or write burst is prohibited for burst length of 4 and only allowed for burst length of 8

under the following conditions:

1. A Read Burst of 8 can only be interrupted by another Read command. Read burst interruption by a Write or Precharge

Command is prohibited.

2. A Write Burst of 8 can only be interrupted by another Write command. Write burst interruption by a Read or Precharge

Command is prohibited.

3. Read burst interrupt must occur exactly two clocks after the previous Read command. Any other Read burst interrupt

timings are prohibited.

4. Write burst interrupt must occur exactly two clocks after the previous Write command. Any other Read burst interrupt

timings are prohibited.

5. Read or Write burst interruption is allowed to any bank inside the DDR2 SDRAM.

6. Read or Write burst with Auto-Precharge enabled is not allowed to be interrupted.

7. Read burst interruption is allowed by a Read with Auto-Precharge command.

8. Write burst interruption is allowed by a Write with Auto-Precharge command.

9. All command timings are referenced to burst length set in the mode register. They are not referenced to the actual

burst. For example, Minimum Read to Precharge timing is AL + BL/2 where BL is the burst length set in the mode reg-

ister and not the actual burst (which is shorter because of interrupt). Minimum Write to Precharge timing is WL + BL/ 2

+ tWR, where tWR starts with the rising clock after the un-interrupted burst end and not form the end of the actual burst

end.

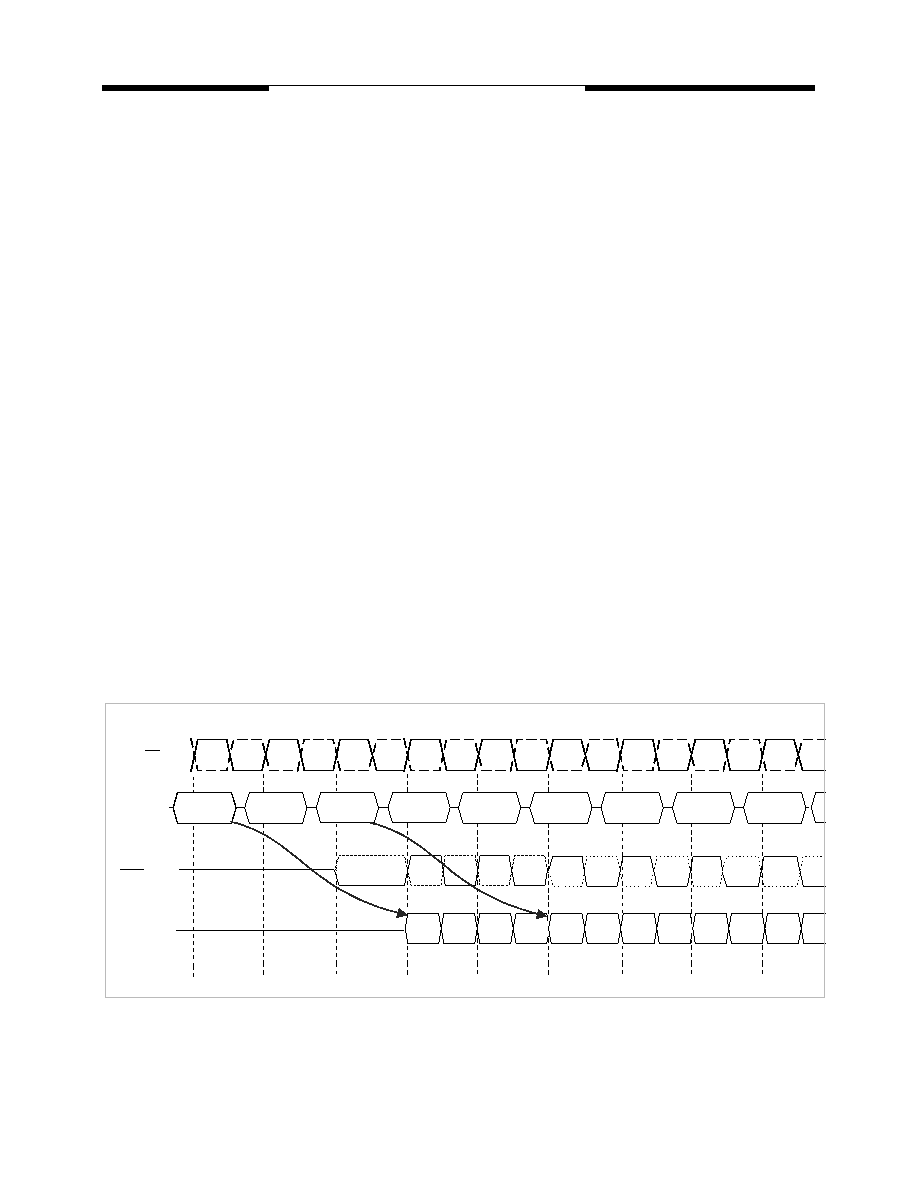

Read Burst Interrupt Timing Example : (CL = 3, AL = 0, RL = 3, BL = 8)

NOP

READ A

T0

T2

T1

T3

T4

T5

T6

T7

T8

CMD

DQ

RBI

DQS,

DQS

READ B

NOP

Dout A0

Dout A1

Dout A2

Dout A3 Dout B0

Dout B1

Dout B2

Dout B3 Dout B4

Dout B5

Dout B6

Dout B

CK, CK

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| V59C1G01804QALF19 | 128M X 8 DDR DRAM, PBGA68 |

| V59C1G01804QALF25A | 128M X 8 DDR DRAM, PBGA68 |

| V59C1G01804QAUJ19AH | 128M X 8 DDR DRAM, PBGA68 |

| V59C1G01804QAUJ25AI | 128M X 8 DDR DRAM, PBGA68 |

| V59C1G01808QALF19E | 128M X 8 DDR DRAM, BGA68 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| V5A010CB | 制造商:Honeywell Sensing and Control 功能描述:MICROSWITCH V5 PIN PLUNGER |

| V5A010CB | 制造商:Honeywell Sensing and Control 功能描述:MICROSWITCH V5 PIN PLUNGER |

| V5A010CB4D | 制造商:Honeywell Sensing and Control 功能描述:MICROSWITCH V5 ROLLER LEVER |

| V5A010CB4D | 制造商:Honeywell Sensing and Control 功能描述:MICROSWITCH V5 ROLLER LEVER |

| V5A010CB4E | 制造商:Honeywell Sensing and Control 功能描述:MICROSWITCH V5 ROLLER LEVER |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。