- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄368672 > TMS320F240PQS 16-Bit Microcontroller PDF資料下載

參數(shù)資料

| 型號: | TMS320F240PQS |

| 英文描述: | 16-Bit Microcontroller |

| 中文描述: | 16位微控制器 |

| 文件頁數(shù): | 35/105頁 |

| 文件大?。?/td> | 1481K |

| 代理商: | TMS320F240PQS |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁當(dāng)前第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁

TMS320C240, TMS320F240

DSP CONTROLLERS

SPRS042D – OCTOBER 1996 – REVISED NOVEMBER 1998

35

POST OFFICE BOX 1443

HOUSTON, TEXAS 77251–1443

multiplier (continued)

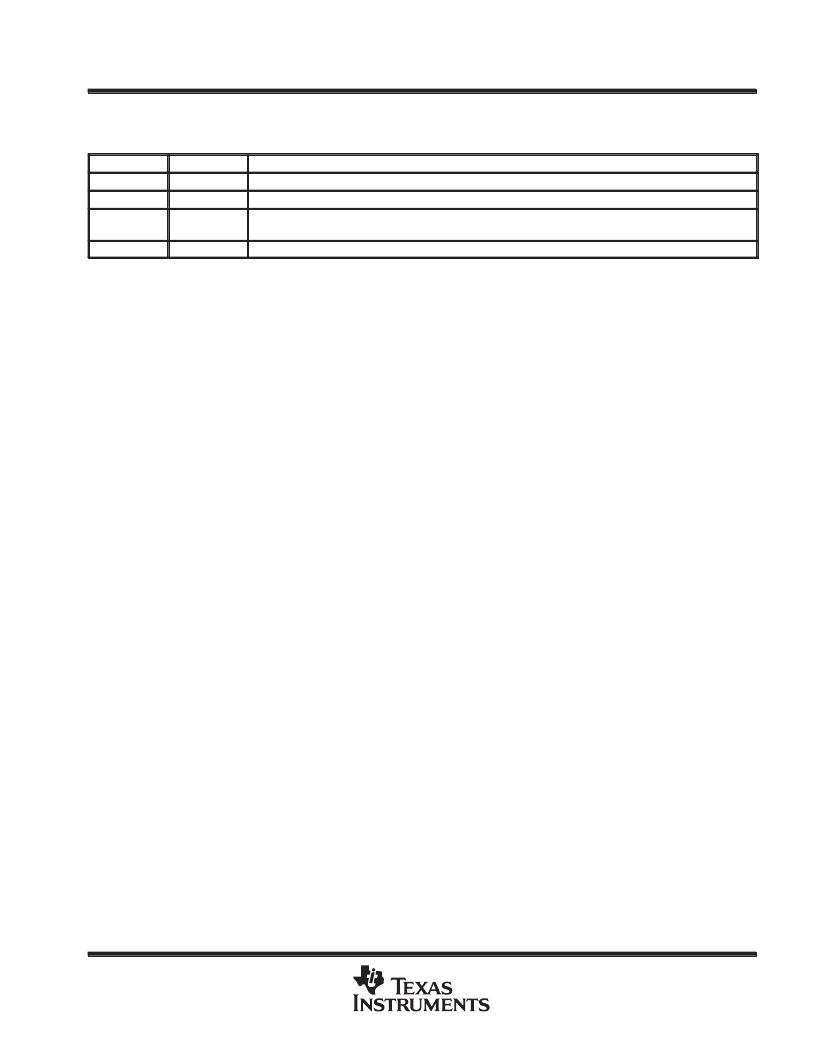

Table 12. PSCALE Product Shift Modes

PM

SHIFT

DESCRIPTION

00

No shift

Product feed to CALU or data bus with no shift

01

Left 1

Removes the extra sign bit generated in a 2s-complement multiply to produce a Q31 product

10

Left 4

Removes the extra 4 sign bits generated in a 16x13 2s-complement multiply to a produce a Q31 product

when using the multiply by a 13-bit constant

11

Right 6

Scales the product to allow up to 128 product accumulation without the possibility of accumulator overflow

The product can be shifted one bit to compensate for the extra sign bit gained in multiplying two 16-bit

2s-complement numbers (MPY instruction). A four-bit shift is used in conjunction with the MPY instruction with

a short immediate value (13 bits or less) to eliminate the four extra sign bits gained in multiplying a 16-bit number

by a 13-bit number. Finally, the output of PREG can be right-shifted 6 bits to enable the execution of up to

128 consecutive multiply/accumulates without the possibility of overflow.

The LT (load TREG) instruction normally loads TREG to provide one operand (from the data bus), and the MPY

(multiply) instruction provides the second operand (also from the data bus). A multiplication also can be

performed with a 13-bit immediate operand when using the MPY instruction. Then a product is obtained every

two cycles. When the code is executing multiple multiplies and product sums, the CPU supports the pipelining

of the TREG load operations with CALU operations using the previous product. The pipeline operations that

run in parallel with loading the TREG include: load ACC with PREG (LTP); add PREG to ACC (LTA); add PREG

to ACC and shift TREG input data (DMOV) to next address in data memory (LTD); and subtract PREG from ACC

(LTS).

Two multiply/accumulate instructions (MAC and MACD) fully utilize the computational bandwidth of the

multiplier, allowing both operands to be processed simultaneously. The data for these operations can be

transferred to the multiplier each cycle by way of the program and data buses. This facilitates single-cycle

multiply/accumulates when used with the repeat (RPT) instruction. In these instructions, the coefficient

addresses are generated by program address generation (PAGEN) logic, while the data addresses are

generated by data address generation (DAGEN) logic. This allows the repeated instruction to access the values

from the coefficient table sequentially and step through the data in any of the indirect addressing modes.

The MACD instruction, when repeated, supports filter constructs (weighted running averages) so that as the

sum-of-products is executed, the sample data is shifted in memory to make room for the next sample and to

throw away the oldest sample.

The MPYU instruction performs an unsigned multiplication, which greatly facilitates extended-precision

arithmetic operations. The unsigned contents of TREG are multiplied by the unsigned contents of the addressed

data memory location, with the result placed in PREG. This process allows the operands of greater than 16 bits

to be broken down into 16-bit words and processed separately to generate products of greater than 32 bits. The

SQRA (square/add) and SQRS (square/subtract) instructions pass the same value to both inputs of the

multiplier for squaring a data memory value.

After the multiplication of two 16-bit numbers, the 32-bit product is loaded into the 32-bit product register

(PREG). The product from PREG can be transferred to the CALU or to data memory by way of the SPH (store

product high) and SPL (store product low). Note: the transfer of PREG to either the CALU or data bus passes

through the PSCALE shifter, and therefore is affected by the product shift mode defined by PM. This is important

when saving PREG in an interrupt-service-routine context save as the PSCALE shift effects cannot be modeled

in the restore operation. PREG can be cleared by executing the MPY #0 instruction. The product register can

be restored by loading the saved low half into TREG and executing a MPY #1 instruction. The high half, then,

is loaded using the LPH instruction.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| TMS320LC31-40 | Digital Signal Processor |

| TMS320LC53PQ | 16-Bit Digital Signal Processor |

| TMP320C51HQ | Transient Voltage Suppressor Diodes |

| TMS320C50PQA40 | 16-Bit Digital Signal Processor |

| TMS320C51PQA40 | 16-Bit Digital Signal Processor |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| TMS320F241FN | 功能描述:數(shù)字信號處理器和控制器 - DSP, DSC 16B 5V fixed point DSP w/ Flash RoHS:否 制造商:Microchip Technology 核心:dsPIC 數(shù)據(jù)總線寬度:16 bit 程序存儲器大小:16 KB 數(shù)據(jù) RAM 大小:2 KB 最大時鐘頻率:40 MHz 可編程輸入/輸出端數(shù)量:35 定時器數(shù)量:3 設(shè)備每秒兆指令數(shù):50 MIPs 工作電源電壓:3.3 V 最大工作溫度:+ 85 C 封裝 / 箱體:TQFP-44 安裝風(fēng)格:SMD/SMT |

| TMS320F241FN | 制造商:Texas Instruments 功能描述:IC C2000 DSP SMD 320F241 PLCC68 |

| TMS320F241FNA | 功能描述:數(shù)字信號處理器和控制器 - DSP, DSC 16B 5V fixed point DSP w/ Flash RoHS:否 制造商:Microchip Technology 核心:dsPIC 數(shù)據(jù)總線寬度:16 bit 程序存儲器大小:16 KB 數(shù)據(jù) RAM 大小:2 KB 最大時鐘頻率:40 MHz 可編程輸入/輸出端數(shù)量:35 定時器數(shù)量:3 設(shè)備每秒兆指令數(shù):50 MIPs 工作電源電壓:3.3 V 最大工作溫度:+ 85 C 封裝 / 箱體:TQFP-44 安裝風(fēng)格:SMD/SMT |

| TMS320F241FNS | 功能描述:數(shù)字信號處理器和控制器 - DSP, DSC 16B 5V fixed point DSP w/ Flash RoHS:否 制造商:Microchip Technology 核心:dsPIC 數(shù)據(jù)總線寬度:16 bit 程序存儲器大小:16 KB 數(shù)據(jù) RAM 大小:2 KB 最大時鐘頻率:40 MHz 可編程輸入/輸出端數(shù)量:35 定時器數(shù)量:3 設(shè)備每秒兆指令數(shù):50 MIPs 工作電源電壓:3.3 V 最大工作溫度:+ 85 C 封裝 / 箱體:TQFP-44 安裝風(fēng)格:SMD/SMT |

| TMS320F241PG | 功能描述:數(shù)字信號處理器和控制器 - DSP, DSC 16B 5V fixed point DSP w/ Flash RoHS:否 制造商:Microchip Technology 核心:dsPIC 數(shù)據(jù)總線寬度:16 bit 程序存儲器大小:16 KB 數(shù)據(jù) RAM 大小:2 KB 最大時鐘頻率:40 MHz 可編程輸入/輸出端數(shù)量:35 定時器數(shù)量:3 設(shè)備每秒兆指令數(shù):50 MIPs 工作電源電壓:3.3 V 最大工作溫度:+ 85 C 封裝 / 箱體:TQFP-44 安裝風(fēng)格:SMD/SMT |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。