- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄361342 > T35L6432A-5Q (TM Technology, Inc.) 64K x 32 SRAM PDF資料下載

參數(shù)資料

| 型號: | T35L6432A-5Q |

| 廠商: | TM Technology, Inc. |

| 英文描述: | 64K x 32 SRAM |

| 中文描述: | 64K的× 32的SRAM |

| 文件頁數(shù): | 11/15頁 |

| 文件大小: | 1347K |

| 代理商: | T35L6432A-5Q |

TE

CH

tm

T35L6432A

Taiwan Memory Technology, Inc. reserves the right

P. 11

to change products or specifications without notice.

Publication Date: DEC. 1998

Revision:A

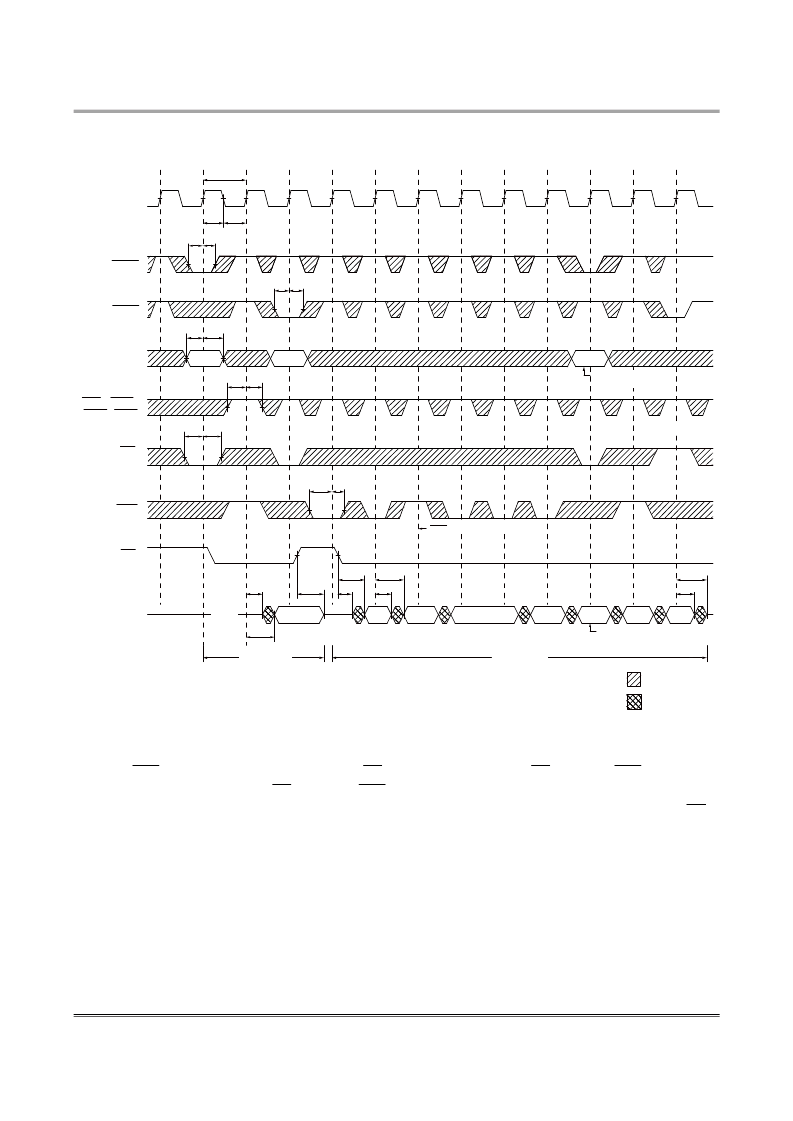

READ TIMING

Hig h-Z

BUR S T RE AD

C L K

A DS C

A D S P

A D DR E S S

G W , B W E ,

B W 1 -B W 4

t KC

t KH

t KL

t AD SS

t ADS H

DON'T CARE

UNDEFINED

t A DS S

t AD SH

t AS

t AH

t W S

t WH

t CE S

t CE H

t AAS

t AAH

t O EQ

tOEL Z

t KQ X

tOE HZ

t KQ

t KQHZ

t K QX

t KQ

t KQ LZ

S ing le RE AD

(NO TE 3)

Q (A1)

Q (A2)

Q(A2+1)

Q (A2+2)

Q(A2 +3 )

Q (A2+1)

Burst wra ps a round

to its inita l sta te.

AD V s uspe nds burs t.

Burst continue d with

new base addre ss.

Q(A2)

A3

A2

A 1

(NOT E1 )

Des ele ct cy cle.

C E

( N O T E 2 )

ADV

O E

Q

Q(A3)

Note:

1. Q(A2) refers to output from address A2. Q (A2 + 1) refers to output from the next internal burst

address following A2.

2. CE2 and CE2 have timing identical to CE. On this diagram, when CE is LOW, CE2 is LOW and

CE2 is HIGH. When CE is HIGH, CE2 is HIGH and CE2 is LOW.

3. Timing is shown assuming that the device was not enabled before entering into this sequence. OE

does not cause Q to be driven until after the following clock rising edge.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| T35L6432A-5T | 64K x 32 SRAM |

| T35L6432B | 64K x 32 SRAM |

| T35L6432B-10Q | 64K x 32 SRAM |

| T35L6432B-12T | 64K x 32 SRAM |

| T35L6464A | 64K x 64 SRAM |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| T35L6432A-5T | 制造商:TMT 制造商全稱:TMT 功能描述:64K x 32 SRAM |

| T35L6432B | 制造商:TMT 制造商全稱:TMT 功能描述:64K x 32 SRAM |

| T35L6432B-10Q | 制造商:TMT 制造商全稱:TMT 功能描述:64K x 32 SRAM |

| T35L6432B-12T | 制造商:TMT 制造商全稱:TMT 功能描述:64K x 32 SRAM |

| T35L6464A | 制造商:TMT 制造商全稱:TMT 功能描述:64K x 64 SRAM |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。